Ana Claudia de Melo Oliveira;

Ladjane Coelho dos Santos;

Jeane de Souza Costa;

Irai Tadeu Ferreira de Resende;

Gilderlan Rodrigues Oliveira;

Denilson Pereira Gonçalves;

Henrique Nunes de Santana;

Waldiney Giacomelli.

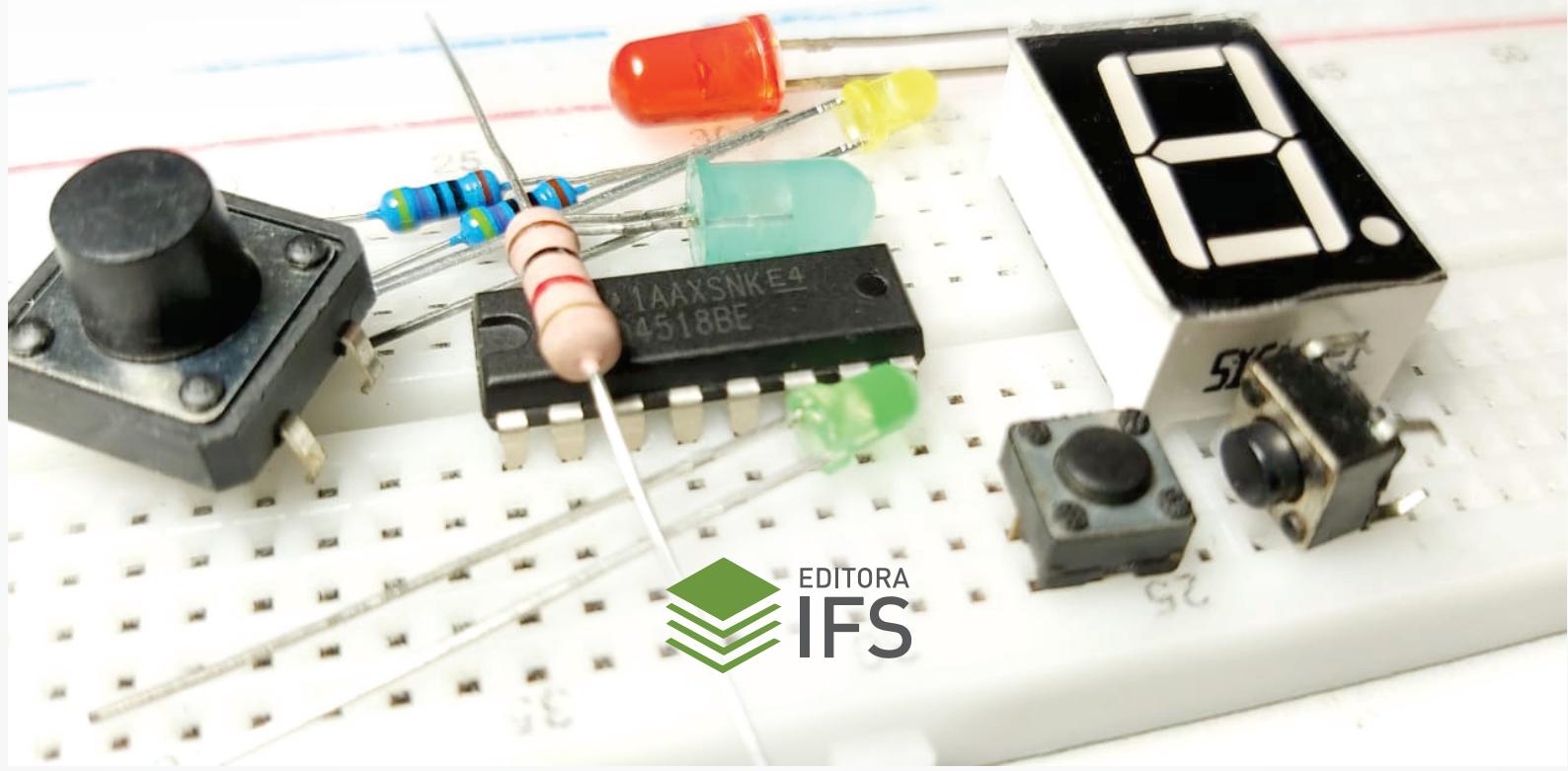

# Guia de Práticas de ELETROÔNICA DIGITAL

# Guia de Práticas de ELETRÔNICA DIGITAL

Aracaju

2021

## **MINISTÉRIO DA EDUCAÇÃO**

**Instituto Federal de Educação, Ciência e Tecnologia de Sergipe**

**Presidente da República**

Jair Messias Bolsonaro

**Ministro da Educação**

Abraham Weintraub

**Secretário da Educação Profissional e Tecnológica**

Ariosto Antunes Culau

**Reitora do IFS**

Ruth Sales Gama de Andrade

**Pró-Reitora de Pesquisa e Extensão**

Chirlaine Cristine Gonçalves

Ana Claudia de Melo Oliveira;

Ladjane Coelho dos Santos;

Jeane de Souza Costa;

Irai Tadeu Ferreira de Resende;

Gilderlan Rodrigues Oliveira;

Denilson Pereira Gonçalves;

Henrique Nunes de Santana;

Waldiney Giacomelli.

# Guia de Práticas de ELETROÔNICA DIGITAL

**Copyright© 2021 - IFS**

Todos os direitos reservados para a Editora IFS. Nenhuma parte desse livro pode ser reproduzida ou transformada em nenhuma forma e por nenhum meio mecânico, incluindo fotocópia, gravação ou qualquer sistema de armazenamento de informação, sem autorização expressa dos autores ou do IFS.

**Editora-chefe (Coordenadora de Publicações)**

Vanina Cardoso Viana Andrade

**Planejamento e Coordenação Gráfica**

Laryssa Mota Santos Silva

**Projeto Gráfico da Capa**

Laryssa Mota Santos Silva

Henrique Nunes de Santana (Fotografia)

**Revisão**

Danielle Silva Telles

**Diagramação**

Laryssa Mota Santos Silva

**Dados Internacionais de Catalogação na Publicação (CIP)**

G943      Guia de práticas de eletrônica digital [recurso eletrônico]. / Ana Claudia de Melo Oliveira... [et al.]. - Aracaju: Editora IFS, 2021.

77p. : il. color

Formato: E-book

ISBN: 978-65-87114-43-9

1. Eletrônica Digital. 2. Guia Prático. 3. Circuitos Integrados. 4. Portas Lógicas.

I. Oliveira, Ana Claudia de Melo. II. Santos, Ladjane Coelho dos. III. Costa, Jeane de Souza. IV. Resende, Irai Tadeu Ferreira de. V. Oliveira, Gilderlan Rodrigues. VI. Gonçalves, Denilson Pereira. VII. Santana, Henrique Nunes de. VIII. Giacomelli, Waldiney [org].

CDU 681.5(036)

Ficha catalográfica elaborada pela bibliotecária Kelly Cristina Barbosa CRB 5/1637

[2021]

**Instituto Federal de Educação, Ciência e Tecnologia de Sergipe (IFS)**

Avenida Jorge Amado, 1551. Loteamento Garcia, Bairro Jardins.

Aracaju/SE. CEP: 49025-330

TEL.: +55 (79) 3711-3222 / e-mail: edifs@ifs.edu.br

Impresso no Brasil

### **Conselho Científico**

|                                                                           |                                                                  |

|---------------------------------------------------------------------------|------------------------------------------------------------------|

| Chirlaine Cristine Gonçalves<br>Pró-reitora de Pesquisa e Extensão        | Adeline Araújo Carneiro Farias<br>Área: Ciências Humanas         |

| Jaime José da Silveira Barros Neto<br>Diretor de Pesquisa e Pós-graduação | Alexandre Santos de Oliveira<br>Área: Ciências Sociais Aplicadas |

| José Wellington Carvalho Vilar<br>Área: Ciências Exatas e da Terra        | João Batista Barbosa<br>Área: Ciências Agrárias                  |

| Diego Lopes Coriolano<br>Área: Engenharias (titular)                      | Manoela Falcon Gallotti<br>Área: Linguística, Letras e Artes     |

| Herbet Alves de Oliveira<br>Área: Engenharias (suplente)                  | Sheyla Alves Rodrigues<br>Área: Ciências Biológicas              |

### **Membros Externos**

|                                               |                                                    |

|-----------------------------------------------|----------------------------------------------------|

| Flor Ernestina Martinez Espinosa -<br>FIOCRUZ | Eliane Maurício Furtado Martins - IF<br>Sudeste MG |

| Odélia Leonor Sanchez de Alsina - UFCG        | Zélia Soares Macedo - UFS                          |

| Mirian Sumica Carneiro Reis - UNILAB          | Mario Ernesto Giroldo Valério - UFS                |

| Claudio Cledson Novães - UEFS                 | Ana Aparecida Vieira de Moura - IFRR               |

| Caique Jordan Nunes Ribeiro - UFS             | Josilene de Souza - IFRN                           |

| Lucas Molina - UFS                            | Charles Dos Santos Estevam - UFS                   |

| Murilo Lopes Martins - IF Sudeste MG          |                                                    |

### **Editoração**

Kelly Cristina Barbosa - Bibliotecária

### **Produção Visual**

Jéssika Lima Santos - Diagramador

Júlio César Nunes Ramiro - Técnico em Artes Gráficas

# **APRESENTAÇÃO**

## **GUIA DE PRÁTICAS DE ELETRÔNICA DIGITAL**

Ana Claudia de Melo Oliveira; Jeane de Souza Costa; Ladjane Coelho dos Santos; Iraí Tadeu Ferreira de Resende; Gilderlan Rodrigues Oliveira; Denilson Pereira Gonçalves; Henrique Nunes de Santana; Waldiney Giacomelli.

O livro Guia de práticas de Eletrônica Digital discorre sobre temas fundamentais para a compreensão de assuntos destinados às práticas em laboratório vinculadas à lógica combinacional e sequencial.

Essa obra é fruto de uma adequação de um Trabalho de Conclusão de Curso da discente Jeane de Souza Costa do Curso Superior de Tecnologia em Automação Industrial do Instituto Federal de Educação, Ciência e Tecnologia de Sergipe, Campus Lagarto, orientação da professora Drª. Ana Claudia de Melo Oliveira e co-orientação da professora Drª. Ladjane Coelho dos Santos. A elaboração desse guia de práticas contou também com a colaboração valiosa dos docentes do Campus Lagarto, Dr. Iraí Tadeu Ferreira de Resende, Dr. Gilderlan Rodrigues Oliveira, Me. Denilson Pereira Gonçalves, assim como também teve a colaboração de docentes de outros Campus, Me. Henrique Nunes de Santana do Campus Itabaiana e o docente Me. Waldiney Giacomelli do Campus Aracaju.

O conhecimento da eletrônica digital na teoria e na prática, é de fundamental importância para entendimento dos conceitos na área de informática, telecomunicações e atividades industriais. A elaboração do guia de práticas para a disciplina de eletrônica digital contribuirá de maneira significativa para os alunos dos Cursos Superiores de Tecnologia em Automação Industrial, Bacharelado em Engenharia Elétrica e cursos técnicos de áreas afins. Diante dessa necessidade, surgiu a ideia de realizar esse guia com atividades práticas na área, para melhorar o rendimento do aluno e propor melhor agilidade e organização no momento da separação do material para a execução da prática. Ao término de cada experimento será solicitado um relatório para cada prática, onde no final do livro (Anexo) consta um modelo de elaboração de relatório, facilitando dessa forma a confecção do mesmo e possibilitando que o aluno exponha suas dificuldades para que assim possam ser discutidas em sala de aula e posteriormente aprimorar seus conhecimentos.

## LISTA DE FIGURAS

|                                                                                                  |    |

|--------------------------------------------------------------------------------------------------|----|

| Figura 1.1 - Identificação da pinagem dos circuitos integrados .....                             | 17 |

| Figura 1.2 - (a) Simbologia e (b) Expressão da Porta AND.....                                    | 19 |

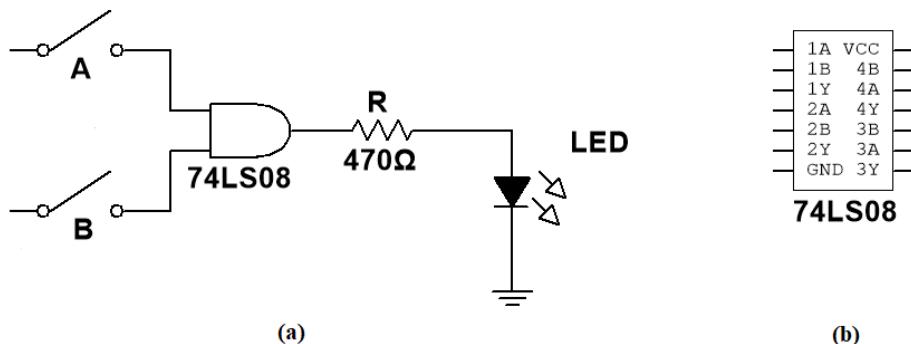

| Figura 1.3 - (a) Circuito lógico (AND) e (b) Configuração do CI 74LS08 ou 4081.....              | 19 |

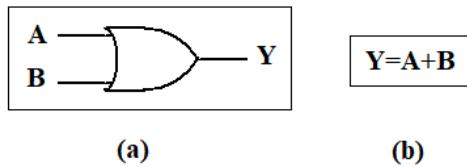

| Figura 1.4 - (a) Simbologia e (b) Expressão da Porta OR.....                                     | 20 |

| Figura 1.5 - (a) Circuito lógico (OR) e (b) Configuração do CI 74LS32 ou 4071.....               | 20 |

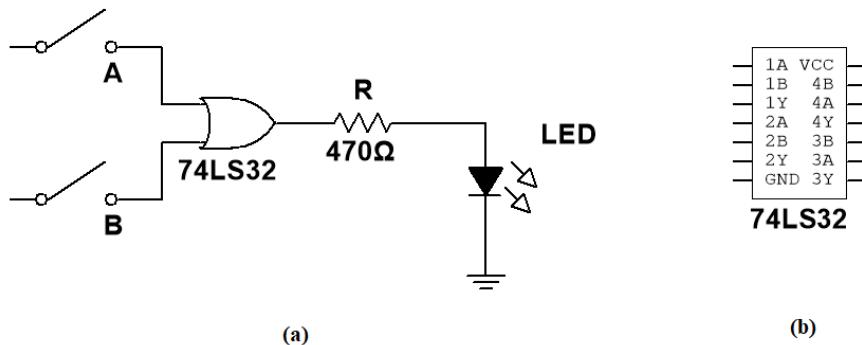

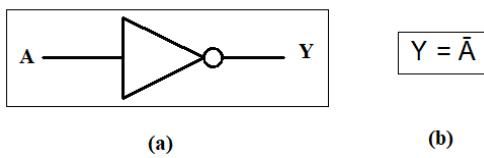

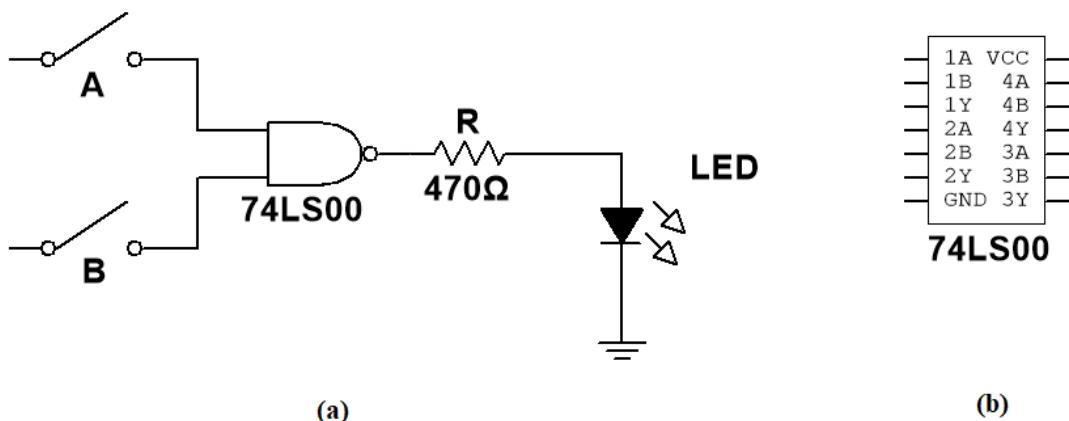

| Figura 1.6 - (a) Simbologia e (b) Expressão da Porta NOT.....                                    | 21 |

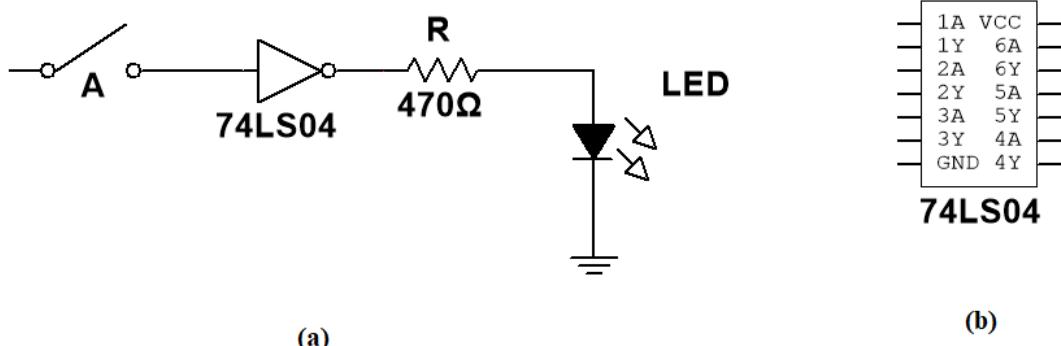

| Figura 1.7 - (a) Circuito lógico (NOT) e (b) Configuração do CI 74LS04 ou 4069.....              | 21 |

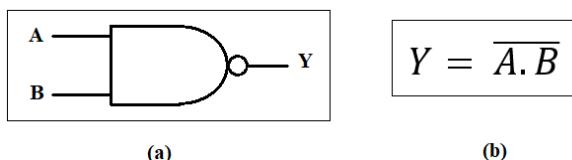

| Figura 1.8 - (a) Simbologia e (b) Expressão da Porta NAND .....                                  | 21 |

| Figura 1.9 - (a) Circuito lógico (NAND) e (b) Configuração do CI 74LS00 ou 4011 ..               | 22 |

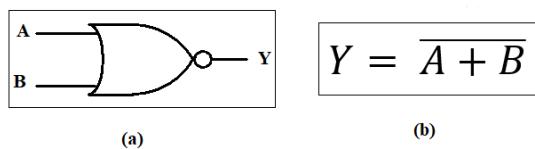

| Figura 1.10 - (a) Simbologia e (b) Expressão da Porta NOR. ....                                  | 22 |

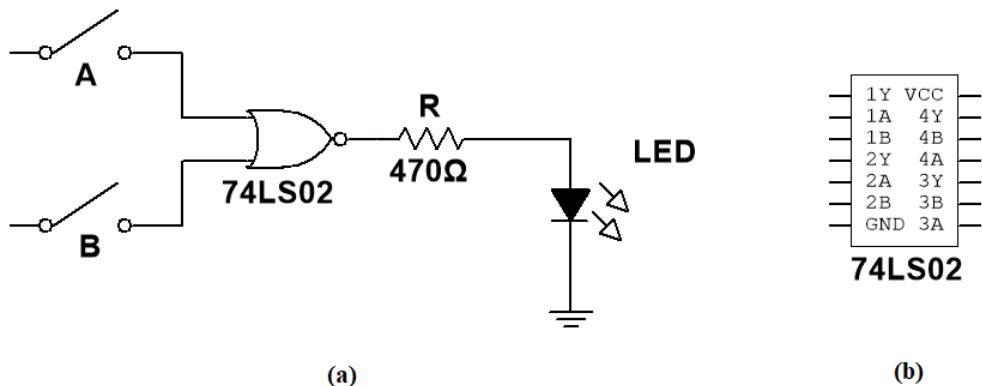

| Figura 1.11 - (a) Circuito lógico (NOR) e (b) Configuração do CI 74LS02 ou 4001 ...              | 23 |

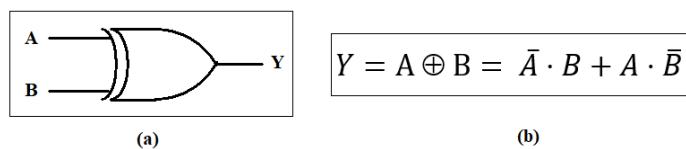

| Figura 1.12 - (a) Simbologia e (b) Expressão da Porta XOR.....                                   | 23 |

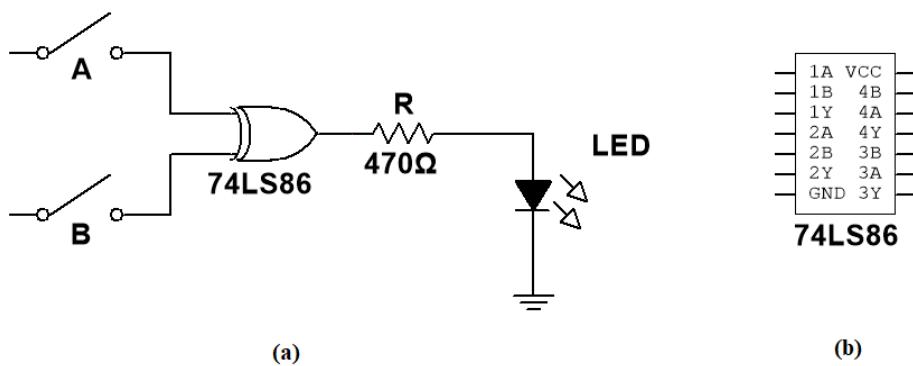

| Figura 1.13 - (a) Circuito lógico (XOR) e (b) Configuração do CI 74LS86 ou 4070....              | 24 |

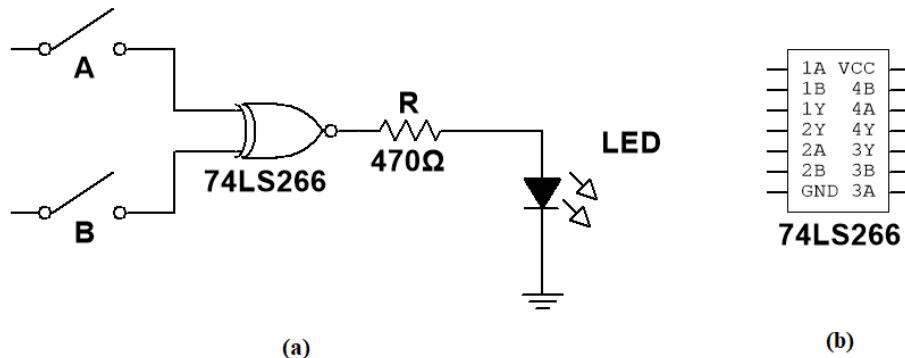

| Figura 1.14 - (a) Simbologia e (b) Expressão da Porta XNOR .....                                 | 24 |

| Figura 1.15 - (a) Circuito lógico (XNOR) e (b) Configuração do CI 74LS266 ou 4077....            | 25 |

| Figura 1.16 - Circuito lógico para teste com a porta NOR.....                                    | 26 |

| Figura 2.1 - Circuito Pisca-Pisca com 74LS00 ou 4011.....                                        | 30 |

| Figura 2.2 - Configuração do CI 74LS00 ou 4011 .....                                             | 30 |

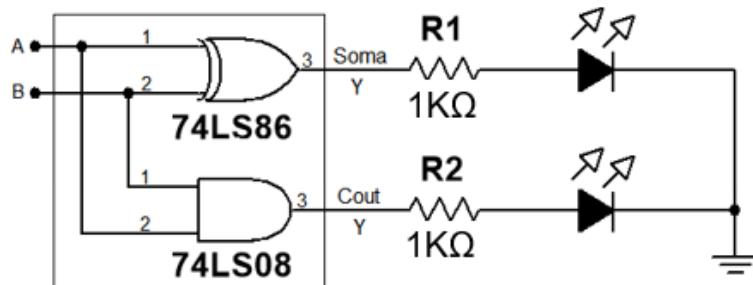

| Figura 3.1 - Circuito lógico Meio Somador .....                                                  | 34 |

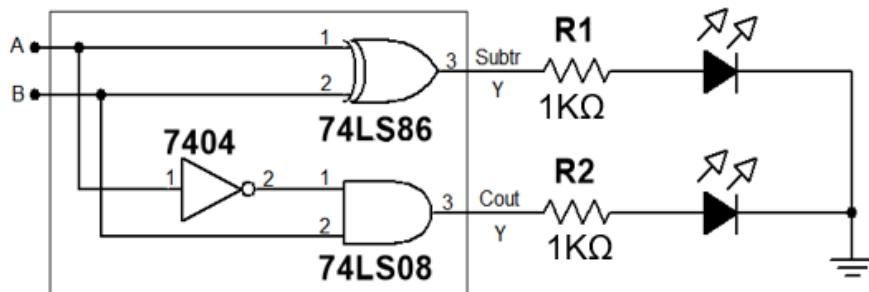

| Figura 3.2 - Circuito lógico Meio Subtrator.....                                                 | 35 |

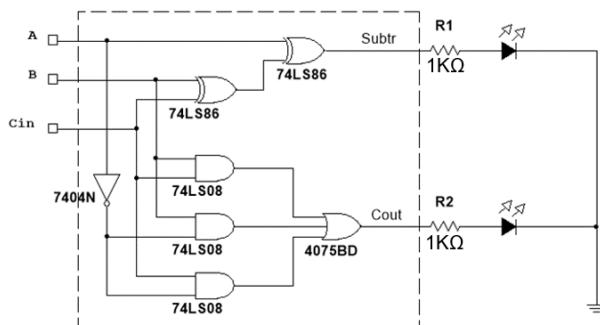

| Figura 3.3 - Circuito lógico Somador completo .....                                              | 36 |

| Figura 3.4 - Circuito lógico Subtrator completo .....                                            | 37 |

| Figura 4.1- Configuração interna do display 7 segmentos. (a) Ânodo comum; (b) Cátodo comum ..... | 40 |

| Figura 4.2– Decodificador CD4511 e display 7 segmentos cátodo comum .....                        | 41 |

| Figura 4.3 - Formato dos dígitos no display de 7 segmentos .....                                 | 42 |

| Figura 4.4 - Pinagem do decodificador CD4511.....                                                | 42 |

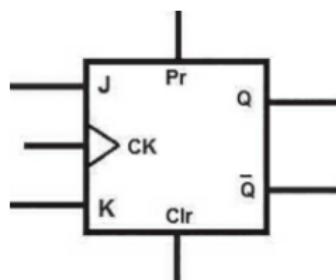

| Figura 5.1 - Simbologia do Flip-flop JK.....                                                     | 46 |

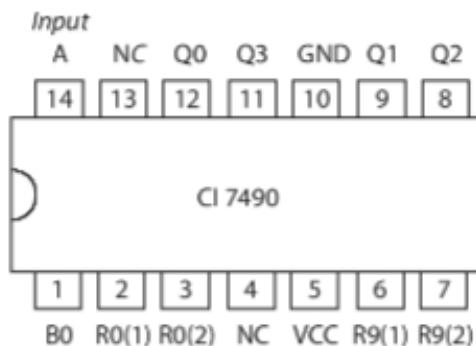

| Figura 5.2 - Configuração do contador 74LS90 .....                                               | 47 |

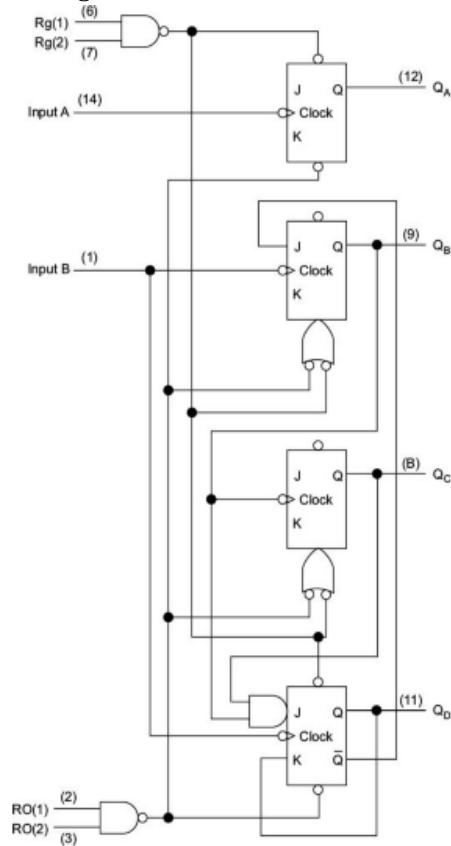

| Figura 5.3 - Diagrama Funcional em blocos do CI 74LS90 .....                                     | 48 |

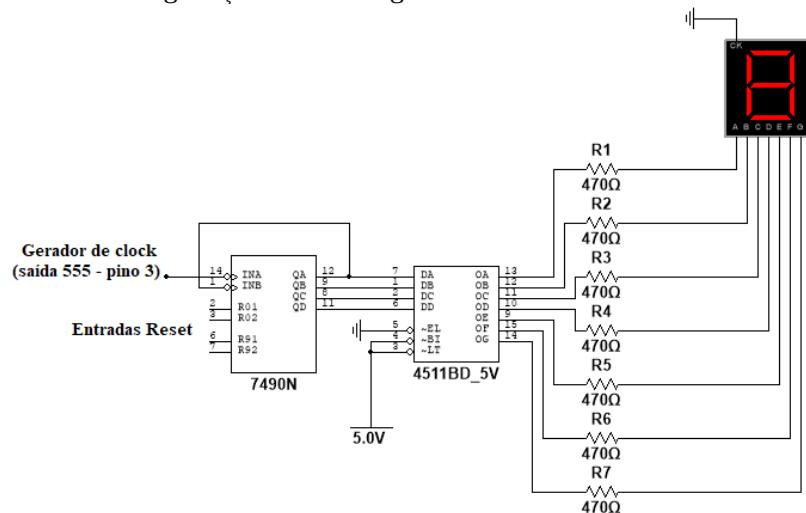

| Figura 5.4 - Configuração da montagem do CI 74LS90 conectado ao CI CD4511 ..                     | 50 |

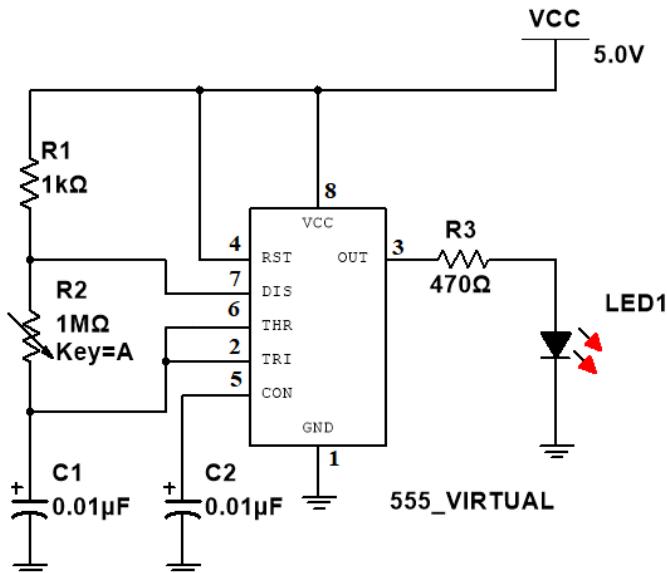

| Figura 5.5 - Gerador de clock com CI 555.....                                                    | 51 |

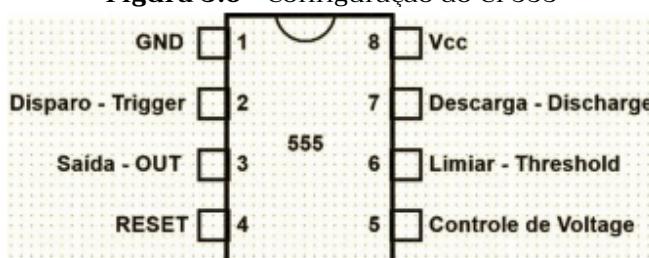

| Figura 5.6 - Configuração do CI 555.....                                                         | 51 |

|                                                                             |    |

|-----------------------------------------------------------------------------|----|

| subida ou (b) por uma borda de descida .....                                | 53 |

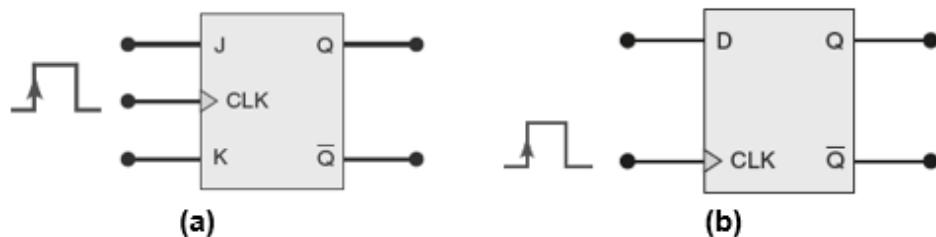

| Figura 6.2 - Flip-Flop (a) JK e (b) D .....                                 | 54 |

| Figura 6.3 - Configuração do Flip-Flop tipo D 7474.....                     | 55 |

| Figura 6.4 - Circuito com Flip-Flop tipo D 7474 .....                       | 55 |

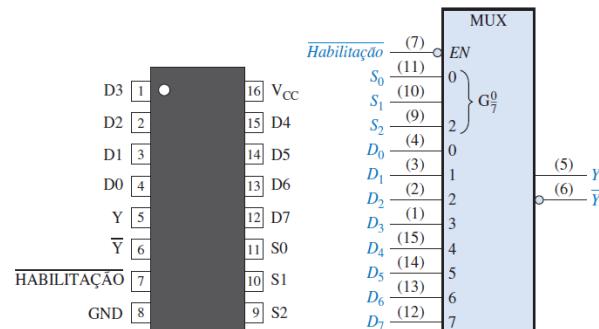

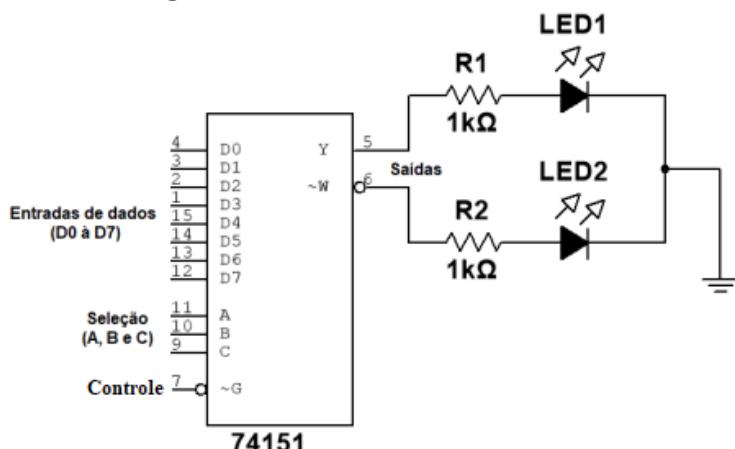

| Figura 7.1 - (a) Diagrama de pinos e (b) símbolo lógico do CI 74LS151 ..... | 58 |

| Figura 7.2 - Circuito com CI 74LS151 .....                                  | 59 |

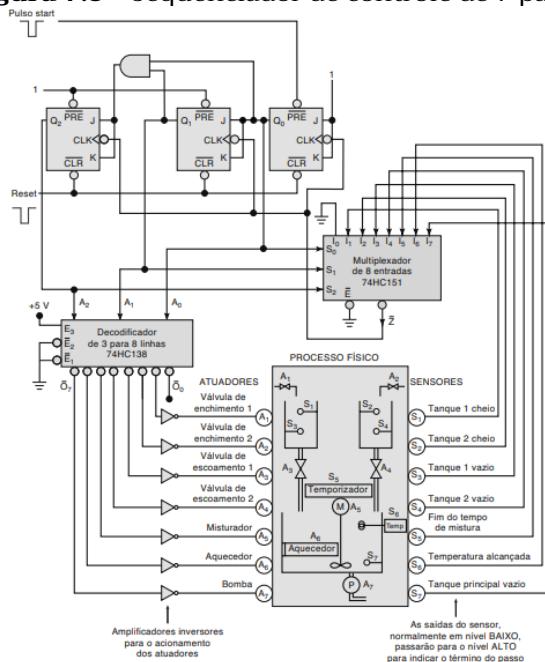

| Figura 7.3 - Sequenciador de controle de 7 passos.....                      | 61 |

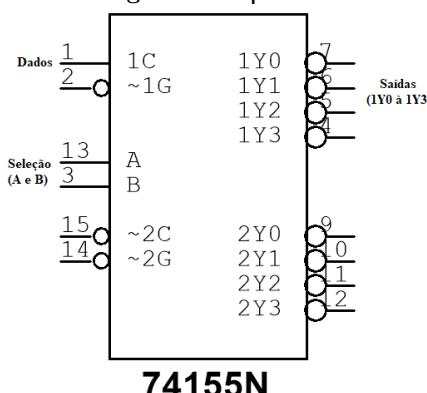

| Figura 8.1 - Diagrama de pinos do CI 74LS155 .....                          | 64 |

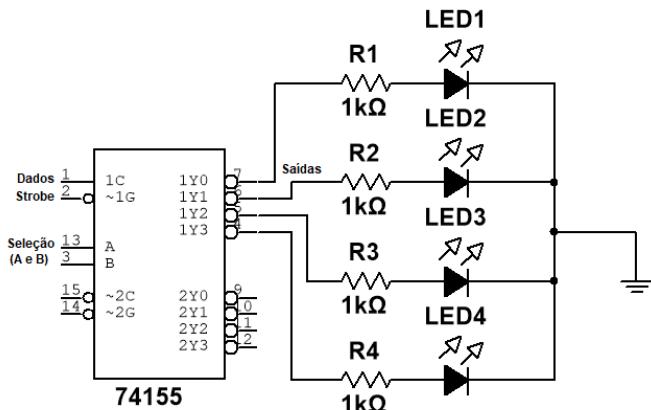

| Figura 8.2 - Circuito com CI 74LS155 .....                                  | 65 |

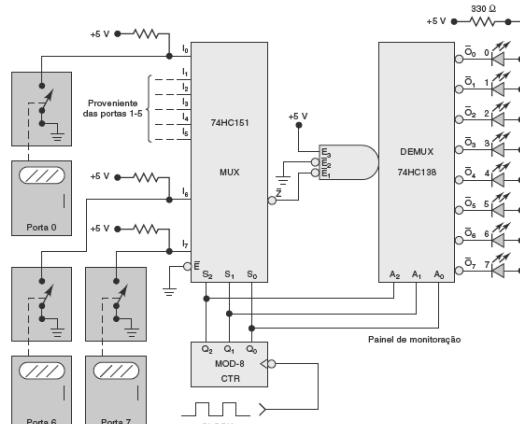

| Figura 8.3 - Sistema de monitoração de segurança.....                       | 66 |

## **LISTA DE TABELAS**

|                                                            |    |

|------------------------------------------------------------|----|

| Tabela 1.1 - Tabela verdade (AND).....                     | 19 |

| Tabela 1.2 - Tabela verdade (OU).....                      | 20 |

| Tabela 1.3 - Tabela verdade (NOT) .....                    | 21 |

| Tabela 1.4 - Tabela verdade (NAND).....                    | 22 |

| Tabela 1.5 - Tabela verdade (NOR).....                     | 23 |

| Tabela 1.6 - Tabela verdade (XOR) .....                    | 24 |

| Tabela 1.7 - Tabela verdade (XNOR) .....                   | 25 |

| Tabela 1.8 - Tabela verdade da expressão booleana (Y)..... | 25 |

| Tabela 1.9 - Tabela verdade (teste com porta NOR) .....    | 26 |

| Tabela 2.1 – Tabela verdade do CI 74LS00.....              | 31 |

| Tabela 3.1 - Circuito lógico Meio somador.....             | 34 |

| Tabela 3.2- Circuito lógico Meio subtrator.....            | 35 |

| Tabela 3.3 - Circuito lógico Somador Completo .....        | 36 |

| Tabela 3.4 - Circuito lógico Subtrator Completo .....      | 37 |

|                                                                               |    |

|-------------------------------------------------------------------------------|----|

| Tabela 4.1 - Comportamento do decodificador CD4511 .....                      | 43 |

| Tabela 5.1 - Tabela de contagem do CI 74LS90 .....                            | 48 |

| Tabela 5.2 - Tabela de reset/contagem do CI 74LS90.....                       | 49 |

| Tabela 6.1 - Funcionamento das entradas e saídas do CI 7474 .....             | 56 |

| Tabela 7.1 - Tabela verdade de funcionamento do CI 74LS151 (referência).....  | 60 |

| Tabela 7.2 - Tabela verdade de funcionamento do CI 74LS151 (comparativa)..... | 60 |

| Tabela 8.1 - Tabela verdade de funcionamento do CI 74LS155 (referência).....  | 65 |

| Tabela 8.2 - Tabela verdade de funcionamento do CI 74LS155 (comparativa)..... | 66 |

## LISTA DE SIGLAS

**TTL:** Lógica de Transistores e Transistores

**CMOS:** Metal-óxido Semicondutor Complementar

**AND:** E

**OR:** Ou

**NOT:** Não

**NAND:** Não E

**NOR:** Não Ou

**MUX:** Multiplexador

**DEMUX:** Demultiplexador

**CI:** Circuito integrado

**LED:** Diodo emissor de luz

**DC:** Corrente contínua

**ULA:** Unidade Lógica Aritmética

**BCD:** Decimal codificado em binário

**FF:** Flip-Flop

# SUMÁRIO

---

|                                                     |    |

|-----------------------------------------------------|----|

| INTRODUÇÃO.....                                     | 13 |

| EXPERIMENTO N°1 - PORTAS LÓGICAS.....               | 16 |

| OBJETIVOS .....                                     | 17 |

| MATERIAL EXPERIMENTAL .....                         | 17 |

| PROCEDIMENTO .....                                  | 18 |

| EXPERIMENTO N°2 - PISCA-PISCA 7400 [Aplicação]..... | 28 |

| OBJETIVOS .....                                     | 29 |

| MATERIAL EXPERIMENTAL .....                         | 29 |

| PROCEDIMENTO .....                                  | 29 |

| EXPERIMENTO N°3 - CIRCUITOS ARITMÉTICOS.....        | 32 |

| OBJETIVO.....                                       | 33 |

| MATERIAL EXPERIMENTAL .....                         | 33 |

| PROCEDIMENTO .....                                  | 34 |

| Círculo Lógico (Meio Somador).....                  | 34 |

| Círculo Lógico (Meio Subtrator) .....               | 35 |

| Círculo Lógico (Somador Completo) .....             | 36 |

| Círculo Lógico (Subtrator Completo) .....           | 37 |

| EXPERIMENTO N°4 - DECODIFICADORES.....              | 39 |

| OBJETIVOS .....                                     | 40 |

| MATERIAL EXPERIMENTAL .....                         | 41 |

| PROCEDIMENTO .....                                  | 41 |

|                                                                    |    |

|--------------------------------------------------------------------|----|

| EXPERIMENTO N°5 - CONTADORES .....                                 | 45 |

| OBJETIVOS .....                                                    | 47 |

| MATERIAL EXPERIMENTAL .....                                        | 47 |

| PROCEDIMENTO .....                                                 | 47 |

| Montagem.....                                                      | 49 |

| EXPERIMENTO N°6 - FLIP-FLOP TIPO D .....                           | 52 |

| OBJETIVO.....                                                      | 54 |

| MATERIAL EXPERIMENTAL .....                                        | 54 |

| PROCEDIMENTO .....                                                 | 54 |

| EXPERIMENTO N°7 - MULTIPLEXADORES.....                             | 57 |

| OBJETIVO.....                                                      | 58 |

| MATERIAL EXPERIMENTAL .....                                        | 58 |

| PROCEDIMENTO .....                                                 | 58 |

| <u>Curiosidade:</u> Aplicação de multiplexadores na indústria..... | 61 |

| EXPERIMENTO N°8 - DEMULTIPLEXADORES.....                           | 63 |

| OBJETIVO.....                                                      | 64 |

| MATERIAL EXPERIMENTAL .....                                        | 64 |

| PROCEDIMENTO .....                                                 | 64 |

| Curiosidade: Aplicação de demultiplexadores na indústria .....     | 66 |

| EXPERIMENTO N°9 - PROJETO FINAL DA DISCIPLINA (INSTRUÇÕES).....    | 68 |

# INTRODUÇÃO

O uso da tecnologia está presente diretamente nas atividades diárias do ser humano, os processos industriais estão presentes desde alimentação ao entretenimento. A digitalização das informações, a ampliação da capacidade de armazenamento de informações, o aumento da velocidade de processamento dos computadores, a miniaturização dos componentes são alguns exemplos dos desafios a serem vencidos na tecnologia (GARCIA e MARTINI, 2018).

Nesse trabalho, o termo “Guia de Práticas” tem um sentido amplo, incluindo atividades laboratoriais, definição de componentes eletrônicos, assim como assuntos abordados na disciplina de eletrônica digital, beneficiando tanto os professores como os alunos dos cursos Superiores de Engenharia Elétrica e Tecnologia em Automação Industrial como também dos cursos técnicos de áreas afins.

Esse guia tem como objetivo promover ao aluno a habilidade de desenvolver práticas experimentais de maneira eficiente, garantindo e consolidando o aprendizado do aluno.

Trata-se de um guia formado por 8 experiências com estrutura prática, constituídas das seguintes etapas: breve introdução teórica sobre cada tema, objetivos, material experimental utilizado e o procedimento da experiência.

Dentre os assuntos abordados, o presente trabalho dar-se início com as portas-lógicas, as quais têm informações básicas sobre os princípios da eletrônica digital. As famílias lógicas utilizadas estão divididas em dois grandes grupos: Lógica de Transistores e Transistores (TTL) e Transistores de efeito de Campo MOS canal N e canal P (CMOS); logo a família TTL funciona com tensão de alimentação padronizada em 5V e são disponibilizadas em duas versões: a comercial, cuja nomenclatura da série inicia-se com 74XX e a versão militar com a série 54XX. A família CMOS, possui como principal característica a flexibilidade de operar com tensões que se estende de 3 à 15V e mantém a mesma pinagem dos circuitos integrados da família TTL (CARVALHO e SILVA, 2015).

Na configuração de um circuito digital, o sinal aparece na forma de um pulso elétrico, ou seja, somente existem dois níveis de tensão: nível alto (presença do pulso) e nível baixo (ausência do pulso). Logo, o nível alto é chamado de “1”, e o baixo, de “0”. A menor unidade correspondente à informação que pode ser armazenada ou transmitida é chamada de bit (SZAJNBERG e MORDKA, 2014).

O guia também relata os circuitos aritméticos, que demonstram atividades com operações lógicas elementares, trabalhando com números binários, efetuando adição e subtração dos mesmos. Também são demonstradas experiências com o uso de decodificadores, contadores e flip-flops, que estão normalmente interligados nas suas

aplicações. Os flip-flops armazenam resultados temporários e suas principais aplicações são os registradores e contadores. Os decodificadores são capazes de transformar sinais binários em sinais decimais, já os contadores, por sua vez, possuem estruturas sequenciais, realizando transições de forma sincronizada ou não.

Por último, os multiplexadores (MUX) e demultiplexadores (DEMUX), que são circuitos que funcionam realizando operações combinacionais, muito utilizadas nos computadores, comunicações e sistemas digitais. O multiplexador é um dispositivo que seleciona uma das entradas de dados para a saída em função das entradas de endereçamento, já o demultiplexador endereça apenas uma única entrada de dados para uma das saídas.

Enfim, conclui-se que o guia atende as necessidades do professor e do aluno, no sentido de priorizar sua interação com o laboratório, desde que se adquira o embasamento teórico necessário para a realização da parte experimental.

## EXPERIMENTO N° 1

### PORTAS LÓGICAS

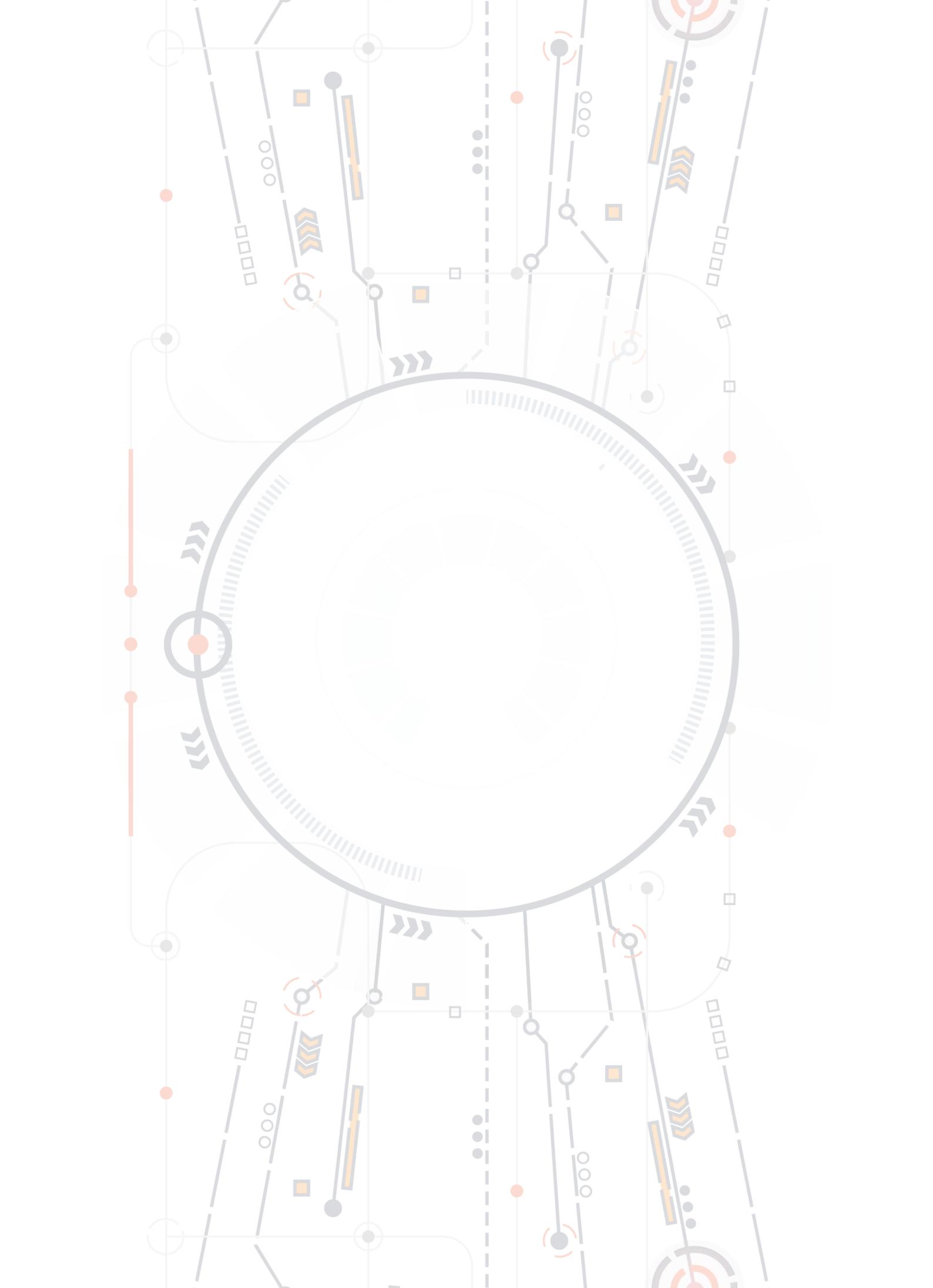

Sabe-se que todos os circuitos digitais, por mais complexos que sejam, são obtidos através de portas lógicas. As portas lógicas, por sua vez, não são encontradas comercialmente de uma forma discreta (como os resistores) e sim encapsuladas em circuitos Integrados – CI’s. Todo circuito integrado possui um conjunto de contatos externos, denominados “pinos” (leds ou ainda terminais), cada qual com sua função específica. Os pinos são numerados a partir do chanfro ou rebaixo que fica na parte externa do componente, a partir do número “1” no sentido anti-horário, conforme apresentado na Figura 1.1 (NETO e OLIVEIRA, 2020). Todo circuito integrado possui um manual (folha de dados) no qual a função de cada um de seus pinos está descrita no mesmo. Os CI’s que implementam funções lógicas podem possuir uma ou mais portas, geralmente todas de uma mesma função.

**Figura 1.1** - Identificação da pinagem dos circuitos integrados

**Fonte:** TOKHEIM, 2013

## OBJETIVOS

- Familiarizar-se com o uso de circuitos integrados no que se refere a sua identificação e pinagens;

- Utilizar circuitos integrados na construção de funções lógicas;

- Utilizar o LED como verificador de estado lógico;

- Realizar montagem e testar o funcionamento do circuito.

## MATERIAL EXPERIMENTAL

- ProtoBoard;

- Fonte de tensão DC (TTL: 5V);

- Resistor:  $470\Omega$ ;

- LED's;

- Circuitos integrados TTL (74LSXX) ou CMOS referentes à cada porta lógica;

- Chaves;

- Alicates;

- Condutores para conexão;

- Multímetro digital.

## PROCEDIMENTO

► Teste o funcionamento das portas lógicas abaixo, seguindo os seguintes procedimentos:

- Preencha a tabela verdade para auxílio na verificação prática;

- Inserir nível alto (1) ou baixo (0) em uma das entradas do circuito integrado de acordo com as condições da tabela verdade;

- A alimentação do circuito deverá ser em 5V (TTL) corrente contínua, caso possua CI da família CMOS pode usar também, pois a pinagem é a mesma da família TTL;

- Verifique o nível lógico na saída de cada porta lógica de acordo com as condições da tabela verdade;

- IMPORTANTE:** Após a montagem chame o(a) professor(a), e peça-o(a) que confira a ligação e, em seguida, energize o circuito.

- Fotografe todos os resultados, e os inclua no relatório final.

### • Porta AND (E)

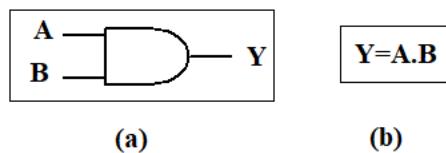

No funcionamento da porta AND, a saída é igual a “1” se todas as entradas estiverem em nível alto “1”. A saída é igual a “0” se ao menos uma entrada for “0”, se todas as entradas não forem “1” (CAPUANO e IDOETA, 2012). O circuito integrado mais comum na família TTL é o 74LS08 e na família CMOS é o 4081 (CARVALHO e SILVA, 2015). Segue a simbologia, expressão e funcionamento da porta AND conforme apresentados na Figura 1.2, Tabela 1.1 e na Figura 1.3 respectivamente.

**Figura 1.2** - (a) Simbologia e (b) Expressão da Porta AND

**Fonte:** Autores, 2020

**Tabela 1.1** - Tabela verdade (AND)

| Condição | Entradas |   | Saída<br>(teórica) | Saída<br>(prática) |

|----------|----------|---|--------------------|--------------------|

|          | A        | B | Y                  | Y                  |

| 0        |          |   |                    |                    |

| 1        |          |   |                    |                    |

| 2        |          |   |                    |                    |

| 3        |          |   |                    |                    |

**Fonte:** Autores, 2020

**Figura 1.3** - (a) Circuito lógico (AND) e (b) Configuração do CI 74LS08 ou 4081

**Fonte:** Autores, 2020

- Porta OR (OU)

No funcionamento da porta OR, a saída é igual a “1” se pelo menos uma das entradas estiver em nível alto “1”. A saída é igual a “0” se nenhuma entrada for “1”, todas forem “0” (CAPUANO e IDOETA, 2012). O circuito integrado mais comum na família TTL é o 74LS32 e na família CMOS é o 4071 (CARVALHO e SILVA, 2015). Segue a simbologia, expressão e funcionamento da porta OR conforme apresentados na Figura 1.4, Tabela 1.2 e na Figura 1.5 respectivamente.

**Figura 1.4** - (a) Simbologia e (b) Expressão da Porta OR

**Fonte:** Autores, 2020

**Tabela 1.2** - Tabela verdade (OU)

| Condição | Entradas |   | Saída<br>(teórica) | Saída<br>(prática) |

|----------|----------|---|--------------------|--------------------|

|          | A        | B | Y                  | Y                  |

| 0        |          |   |                    |                    |

| 1        |          |   |                    |                    |

| 2        |          |   |                    |                    |

| 3        |          |   |                    |                    |

**Fonte:** Autores, 2020

**Figura 1.5** - (a) Circuito lógico (OR) e (b) Configuração do CI 74LS32 ou 4071

**Fonte:** Autores, 2020

- Porta NOT (NÃO)

No funcionamento da porta NOT, para um determinado valor na entrada, a saída possui um valor contrário ao da entrada. Se a entrada estiver em nível alto “1”, a saída será “0”. Se a entrada for “0”, a saída será “1”, ou seja, para um valor na entrada a saída será seu complemento, ou o inverso do valor na entrada (CAPUANO e IDOETA, 2012). O circuito integrado mais comum na família TTL é o 74LS04 e na família CMOS é o 4069 (CARVALHO e SILVA, 2015). Segue a simbologia, expressão e o funcionamento da porta NOT conforme apresentados na Figura 1.6, Tabela 1.3 e na Figura 1.7 respectivamente.

**Figura 1.6** - (a) Simbologia e (b) Expressão da Porta NOT

**Fonte:** Autores, 2020

**Tabela 1.3 - Tabela verdade (NOT)**

| C o n d i ç ã o | Entrada | Saída<br>(teórica) | Saída<br>(prática) |

|-----------------|---------|--------------------|--------------------|

|                 | A       | Y                  | Y                  |

| 0               |         |                    |                    |

| 1               |         |                    |                    |

**Fonte:** Autores, 2020

**Figura 1.7** - (a) Circuito lógico (NOT) e (b) Configuração do CI 74LS04 ou 4069

**Fonte:** Autores, 2020

- Porta NAND (NÃO E)

No funcionamento da porta NAND, a saída é igual a “0” se todas as entradas estiverem em nível alto “1”. A saída é igual a “1” se ao menos uma entrada for “0”, se todas as entradas não forem “1”. O circuito integrado mais comum na família TTL é o 74LS00 e na família CMOS é o 4011 (CARVALHO e SILVA, 2015). Segue a simbologia, expressão e o funcionamento da porta NAND conforme apresentados na Figura 1.8, Tabela 1.4 e na Figura 1.9 respectivamente.

**Figura 1.8** - (a) Simbologia e (b) Expressão da Porta NAND

**Fonte:** Autores, 2020

**Tabela 1.4 Tabela verdade (NAND)**

| C o n d i ç ã o | Entradas |   | Saída<br>(teórica) | Saída<br>(prática) |

|-----------------|----------|---|--------------------|--------------------|

|                 | A        | B | Y                  | Y                  |

| 0               |          |   |                    |                    |

| 1               |          |   |                    |                    |

| 2               |          |   |                    |                    |

| 3               |          |   |                    |                    |

**Fonte:** Autores, 2020

**Figura 1.9 - (a) Circuito lógico (NAND) e (b) Configuração do CI 74LS00 ou 4011**

**Fonte:** Autores, 2020

### • Porta NOR (NÃO OU)

No funcionamento da porta NOR, a saída é igual a 0 se pelo menos uma das entradas for 1. A saída é igual a 1 se nenhuma entrada for 1, todas forem zero. O circuito integrado mais comum na família TTL é o 74LS02 e na família CMOS é o 4001 (CARVALHO e SILVA, 2015). Segue a simbologia, expressão e o funcionamento da porta NOR conforme apresentados na Figura 1.10, Tabela 1.5 e na Figura 1.11 respectivamente.

**Figura 1.10 - (a) Símbologia e (b) Expressão da Porta NOR.**

**Fonte:** Autores, 2020

**Tabela 1.5** - Tabela verdade (NOR)

| Condição | Entradas |   | Saída<br>(teórica) | Saída<br>(prática) |

|----------|----------|---|--------------------|--------------------|

|          | A        | B | Y                  | Y                  |

| 0        |          |   |                    |                    |

| 1        |          |   |                    |                    |

| 2        |          |   |                    |                    |

| 3        |          |   |                    |                    |

**Fonte:** Autores, 2020.

**Figura 1.11** - (a) Circuito lógico (NOR) e (b) Configuração do CI 74LS02 ou 4001

**Fonte:** Autores, 2020

### • Porta XOR (OU Exclusivo)

No funcionamento da porta XOR, a saída é igual a 0 se todas as variáveis de entradas forem iguais. A saída é igual a 1 quando as variáveis de entrada forem distintas entre si (CAPUANO e IDOETA, 2012). O circuito integrado mais comum na família TTL é o 74LS86 e na família CMOS é o 4070 (CARVALHO e SILVA, 2015). Segue a simbologia, expressão e o funcionamento da porta XOR conforme apresentados na Figura 1.12, Tabela 1.6 e na Figura 1.13 respectivamente.

**Figura 1.12** - (a) Simbologia e (b) Expressão da Porta XOR

**Fonte:** Autores, 2020

**Tabela 1.6** - Tabela verdade (XOR)

| Condição | Entradas |   | Saída<br>(teórica) | Saída<br>(prática) |

|----------|----------|---|--------------------|--------------------|

|          | A        | B | Y                  | Y                  |

| 0        |          |   |                    |                    |

| 1        |          |   |                    |                    |

| 2        |          |   |                    |                    |

| 3        |          |   |                    |                    |

**Fonte:** Autores, 2020

**Figura 1.13** - (a) Circuito lógico (XOR) e (b) Configuração do CI 74LS86 ou 4070

**Fonte:** Autores, 2020

### • Porta XNOR (NÃO OU Exclusivo)

No funcionamento da porta XNOR, a saída é igual a 0 se todas as variáveis de entradas forem distintas. A saída é igual a 1 quando as variáveis de entrada forem iguais (CAPUANO e IDOETA, 2012). O circuito integrado mais comum na família TTL é o 74LS266 e na família CMOS é o 4077 (CARVALHO e SILVA, 2015). Segue a simbologia, expressão e o funcionamento da porta XNOR conforme apresentados na Figura 1.14, Tabela 1.7 e na Figura 1.15 respectivamente.

**Figura 1.14** - (a) Simbologia e (b) Expressão da Porta XNOR

O diagrama (a) mostra o símbolo da porta XNOR, que é similar ao símbolo da porta NOR, mas com os dois terminais de saída interconectados. O diagrama (b) mostra a expressão booleana da porta XNOR:  $Y = A \odot B = \bar{A} \cdot \bar{B} + A \cdot B$ .

**Fonte:** Autores, 2020

**Tabela 1.7 - Tabela verdade (XNOR)**

| Condição | Entradas |   | Saída<br>(teórica) | Saída<br>(prática) |

|----------|----------|---|--------------------|--------------------|

|          | A        | B | Y                  | Y                  |

| 0        |          |   |                    |                    |

| 1        |          |   |                    |                    |

| 2        |          |   |                    |                    |

| 3        |          |   |                    |                    |

**Fonte:** Autores, 2020

**Figura 1.15 - (a) Circuito lógico (XNOR) e (b) Configuração do CI 74LS266 ou 4077**

**Fonte:** Autores, 2020

► De acordo com a expressão booleana (Y) monte o circuito lógico a seguir através de circuitos integrados referentes a cada porta lógica e preencha a Tabela 1.8. Segue a expressão booleana (Y).

|                                                                               |  |

|-------------------------------------------------------------------------------|--|

| <b>Expressão booleana</b>                                                     |  |

| <b>Quantos CI's serão utilizados para realização da montagem? Cite quais.</b> |  |

**Tabela 1.8 - Tabela verdade da expressão booleana (Y)**

| Condição | Entradas |   | Saída<br>(teórica) | Saída<br>(prática) |

|----------|----------|---|--------------------|--------------------|

|          | A        | B | Y                  | Y                  |

| 0        |          |   |                    |                    |

| 1        |          |   |                    |                    |

| 2        |          |   |                    |                    |

| 3        |          |   |                    |                    |

**Fonte:** Autores, 2020

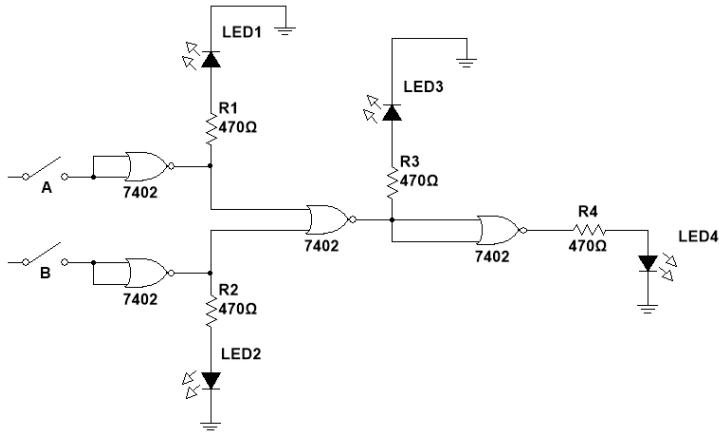

► No circuito da Figura 1.16, execute os seguintes procedimentos a seguir:

**Figura 1.16 - Circuito lógico para teste com a porta NOR**

**Fonte:** Autores, 2020

- Identifique e numere as portas do CI 74HC02;

- Após esta identificação escreva os números dos pinos da porta correspondente do CI 74HC02;

- Escreva na 2<sup>a</sup> linha abaixo de cada porta, a expressão que está saindo de cada uma delas;

- Faça as ligações indicadas na Figura 1.16;

- Opere as chaves A e B conforme indicado nas duas primeiras colunas da Tabela 1.9;

- Preencha a Tabela 1.9 com "0" e "1" para os estados dos LEDs correspondentes.

**Tabela 1.9 - Tabela verdade (teste com porta NOR)**

| Condição | Entradas |   | Saída Porta 1 | Saída Porta 2 | Saída Porta 3 | Saída Porta 4 |

|----------|----------|---|---------------|---------------|---------------|---------------|

|          | A        | B | Y             | Y             | Y             | Y             |

| 0        |          |   |               |               |               |               |

| 1        |          |   |               |               |               |               |

| 2        |          |   |               |               |               |               |

| 3        |          |   |               |               |               |               |

**Fonte:** Autores, 2020

**Logo em seguida responda:**

a) Qual a relação entre o Led1 e a chave A e do Led2 com a chave B?

---

b) O led3 apresenta os valores corretos da função NOR?

---

c) Qual a relação do Led4 com o Led3?

---

► **Anexar relatório à experiência, detalhando:**

- Os componentes utilizados e a respectiva pinagem dos CI's;

- Tabelas preenchidas;

- Fotos das etapas durante a montagem do circuito e etapa final;

- Comentários, discussões e dificuldades encontradas.

**Observação:** No final do livro (Anexo) tem um modelo de elaboração de relatório para auxiliar na confecção do mesmo.

## EXPERIMENTO N° 2 PISCA-PISCA 7400 [Aplicação]

O circuito integrado (CI) 7400 é formado por tecnologia TTL (transistor-transistor-logic), ou seja, Lógica transistor-transistor. O CI 7400 é representado pela função (NÃO E), essa função executa a “multiplicação” lógica de duas ou mais entradas digitais, também chamadas de variáveis booleanas, para então obtermos o valor de sua saída, onde é considerada “falsa” se, e somente se, todas as entradas possuírem nível lógico alto “1” (HAUPT e DACHI, 2018).

## OBJETIVOS

- Familiarizar-se com o uso de circuitos integrados no que se refere a sua identificação e suas pinagens;

- Utilizar Circuitos Integrados na construção de funções lógicas básicas;

- Utilizar o LED como verificador de estado lógico;

- Entender a função dos capacitores no circuito;

- Realizar montagem e testar o funcionamento do circuito.

## MATERIAL EXPERIMENTAL

- ProtoBoard;

- Fonte de tensão DC (TTL: 5V);

- Resistores: 4,7K $\Omega$ ; 100 $\Omega$ ;

- LEDs: 2;

- Capacitores eletrolíticos C<sub>1</sub> e C<sub>2</sub> (10  $\mu$ F à 220  $\mu$ F);

- Circuito integrado TTL (74LS00) ou CMOS (4011);

- Chaves;

- Alicates;

- Condutores para conexão;

- Multímetro digital.

## PROCEDIMENTO

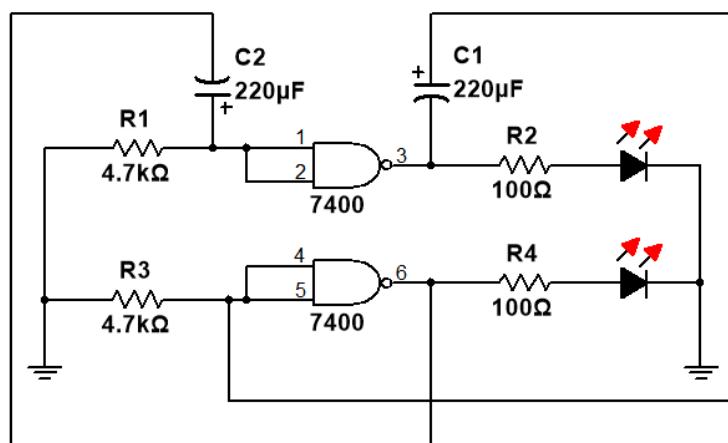

► A frequência das piscadas dos LEDs é determinada pelos capacitores eletrolíticos C<sub>1</sub> e C<sub>2</sub> cujos valores podem ficar entre 10 $\mu$ F e 220 $\mu$ F. A alimentação é direta se a tensão da fonte for de 5V. Apenas metade do circuito integrado é usado, o que significa dizer que outro

pisca-pisca semelhante pode ser “montado” entre os pinos 8 e 13.

a) Monte o circuito da Figura 2.1 e observe a frequência das piscadas conforme variação dos capacitores;

b) **IMPORTANTE:** Após a montagem chame o(a) professor(a), e peça-o(a) que confira a ligação e, em seguida, energize o circuito.

**Figura 2.1** - Circuito Pisca-Pisca com 74LS00 ou 4011

**Fonte:** Autores, 2020

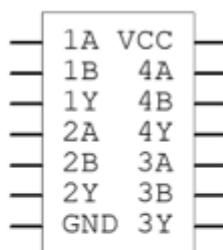

c) **ATENÇÃO:** A alimentação do circuito integrado é no pino 7 (zero = GND, nível baixo) e no pino 14 (5V) (um = Vcc, nível alto), conforme configuração do CI 74LS00 da Figura 2.2.

**Figura 2.2** - Configuração do CI 74LS00 ou 4011

**Simbologia**

**Expressão**

$$Y = \overline{A} \cdot \overline{B}$$

**Fonte:** Autores, 2020

**Tabela 2.1** – Tabela verdade do CI 74LS00

| Condição | Entradas |   | Saída |

|----------|----------|---|-------|

|          | A        | B | Y     |

| 0        | 0        | 0 | 0     |

| 1        | 0        | 1 | 0     |

| 2        | 1        | 0 | 0     |

| 3        | 1        | 1 | 1     |

**Fonte:** Autores, 2020

d) Quais foram os capacitores escolhidos? Ao realizar alterações de valores de capacitores explique o que ocorre no circuito.

Resp.: \_\_\_\_\_

---

---

---

► Anexar relatório à experiência, detalhando:

- Os componentes utilizados e a respectiva pinagem do CI;

- Fotos das etapas durante a montagem do circuito e etapa final;

- Comentários, discussões e dificuldades encontradas.

**Observação:** No final do livro (Anexo) tem um modelo de elaboração de relatório para auxiliar na confecção do mesmo.

## EXPERIMENTO N° 3

### CIRCUITOS ARITIMÉTRICOS

São circuitos combinacionais que realizam operações aritméticas com números binários. Utilizados para construção da ULA (Unidade Lógica Aritmética) de microprocessadores e ainda também encontrados em circuitos integrados comerciais (CAPUANO e IDOETA, 2012).

A vantagem de sistemas digitais é que todas as quantidades podem ser manipuladas rapidamente usando operações numéricas. A ação conjunta da Unidade de Processamento Central (CPU) com a Unidade Lógica Aritmética (ULA) permite realizar as operações de adição, subtração, multiplicação e divisão de números binários as quais são executadas pelos circuitos aritméticos na maioria dos equipamentos digitais. Existem dispositivos mais flexíveis tais como as unidades aritméticas e lógicas “ULA” que são fornecidas na forma de CI’s, e que podem executar diversos tipos de operações, as quais são selecionadas por entradas programáveis (TOKHEIM, 2013).

Os principais circuitos são: meio somador, somador completo, meio subtrator, subtrator completo e somador/subtrator.

**Somador Completo:** Realiza a soma de números de mais de 1 bit.

**Meio Somador:** Possibilita a soma de 2 números binários de 1 bit.

**Subtrator Completo:** Realiza subtração de números de mais de 1 bit.

**Meio Subtrator:** Possibilita a subtração de 2 números binários de 1 bit.

## OBJETIVO

Desenvolver a compreensão de circuitos aritméticos (meio somador e meio subtrator) a partir de portas lógicas.

## MATERIAL EXPERIMENTAL

- ProtoBoard;

- Fonte de tensão DC (TTL: 5V);

- 2 Resistores: 1KΩ;

- LED's: 2;

- Circuitos integrados TTL 7486 (OU exclusivo), 7408 (AND) e 7404 (NOT);

- Chaves;

- Alicates;

- Condutores para conexão;

- Multímetro digital.

## PROCEDIMENTO

► Monte o circuito lógico meio somador da Figura 3.1. Observe os níveis lógicos das saídas, e comprove os resultados obtidos na prática.

**IMPORTANTE:** Após a montagem chame o(a) professor(a), e peça-o(a) que confira a ligação e, em seguida, energize o circuito.

### Circuito Lógico (Meio Somador)

Figura 3.1 - Circuito lógico Meio Somador

Fonte: Autores, 2020

#### a) Lógica do Meio Somador

De acordo com a Tabela 3.1, verifique que o *carry* de saída ( $C_{out}$ ) é 1 apenas quando A e B são 1, ou seja,  $C_{out}$  pode ser expresso como uma operação AND entre as variáveis de entrada ( $C_{out} = A \cdot B$ ). Já a saída soma apresenta nível lógico 1 apenas se as variáveis de entrada, A e B, não forem iguais, ou seja, pode ser expressa como a operação EX-OR entre as variáveis de entrada ( ). (FLOYD, 2007).

b) Após a montagem do circuito lógico meio somador, preencha a Tabela 3.1 para efeito comparativo dos valores teóricos com os valores práticos.

Tabela 3.1 - Circuito lógico Meio somador

| Condição | Entradas |   | Soma<br>(teoria) | $C_{out}$<br>(teoria) | Soma<br>(prática) | $C_{out}$<br>(prática) |

|----------|----------|---|------------------|-----------------------|-------------------|------------------------|

|          | A        | B | Y                | Y                     | Y                 | Y                      |

| 0        | 0        | 0 | 0                | 0                     |                   |                        |

| 1        | 0        | 1 | 1                | 0                     |                   |                        |

| 2        | 1        | 0 | 1                | 0                     |                   |                        |

| 3        | 1        | 1 | 0                | 1                     |                   |                        |

Fonte: Adaptado de GARCIA e MARTINI, 2018

c) Represente as saídas (Soma e  $C_{out}$ ) através de trem de pulsos.

Resp.:

Soma:  $C_{out}:$

► Monte o circuito lógico meio subtrator da Figura 3.2. Observe os níveis lógicos das saídas e comprove os resultados obtidos na prática.

**IMPORTANTE:** Após a montagem chame o(a) professor(a), e peça-o(a) que confira a ligação e, em seguida, energize o circuito.

### Circuito Lógico (Meio Subtrator)

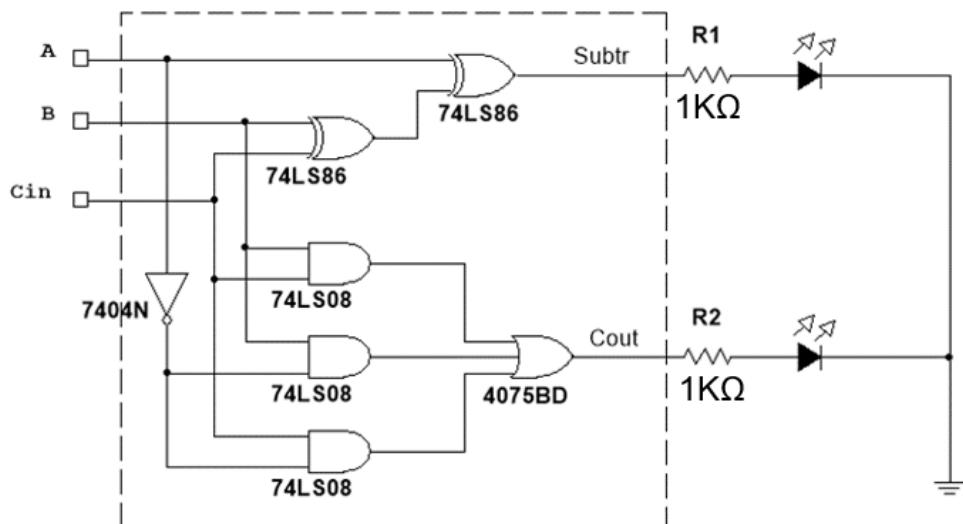

**Figura 3.2 - Circuito lógico Meio Subtrator**

**Fonte:** Autores, 2020

#### a) Lógica do Meio Subtrator

De acordo com a Tabela 3.2, verifique que o *carry* de saída ( $C_{out}$ ) pode ser expresso como uma operação AND e NOT entre as variáveis de entrada ( $C_{out} = \bar{A}B + A\bar{B}$ ). Já a saída *subtr* apresenta nível lógico 1 apenas se as variáveis de entrada, A e B, não forem iguais, ou seja, pode ser expressa como a operação EX-OR entre as variáveis de entrada () (GARCIA e MARTINI, 2018).

**b)** Após a montagem do circuito lógico meio subtrator, preencha a Tabela 3.2 para efeito comparativo dos valores teóricos com os valores práticos.

**Tabela 3.2- Circuito lógico Meio subtrator**

| Condição | Entradas |   | Subtr<br>(teoria) | $C_{out}$<br>(teoria) | Subtr<br>(prática) | $C_{out}$<br>(prática) |

|----------|----------|---|-------------------|-----------------------|--------------------|------------------------|

|          | A        | B |                   |                       |                    |                        |

| 0        | 0        | 0 | 0                 | 0                     |                    |                        |

| 1        | 0        | 1 | 1                 | 1                     |                    |                        |

| 2        | 1        | 0 | 1                 | 0                     |                    |                        |

| 3        | 1        | 1 | 0                 | 0                     |                    |                        |

**Fonte:** Adaptado de GARCIA e MARTINI, 2018

**c)** Represente as saídas (*Subtr* e  $C_{out}$ ) através de trem de pulsos.

**Resp.:**

**Soma:**  $C_{out}:$

**Observação:** Os itens 3.4.3 e 3.4.4 são complementos para os estudos, suas montagens e testes, servem como atividades complementares.

## Circuito Lógico (Somador Completo)

**Figura 3.3 - Circuito lógico Somador completo**

**Fonte:** Autores, 2020

### a) Lógica do Somador Completo

De acordo com a Tabela 3.3, verifique que agora temos um carry de entrada ( $C_{in}$ ) e um carry de saída ( $C_{out}$ ). O carry de saída ( $C_{out}$ ) pode ser expresso como uma operação OR de três operações AND entre as variáveis de entrada ( $C_{out} = (A \cdot B) + (A \cdot C_{in}) + (B \cdot C_{in})$ ). Já a saída soma apresenta nível lógico “1” apenas quando as variáveis de entrada, A, B e  $C_{in}$ , não forem iguais e somente em um caso onde as entradas forem todas nível alto “1”, ou seja, pode ser expressa como a operação EX-OR entre as variáveis de entrada (Soma =  $A \oplus B \oplus C_{in}$ ) (GARCIA e MARTINI, 2018).

**b)** Após a montagem do circuito lógico somador completo, preencha a Tabela 3.3 para efeito comparativo dos valores teóricos com os valores práticos.

**Tabela 3.3 - Circuito lógico Somador Completo**

| Condição | Entradas |   |          | Soma (teoria) | $C_{out}$ (teoria) | Soma (prática) | $C_{out}$ (prática) |

|----------|----------|---|----------|---------------|--------------------|----------------|---------------------|

|          | A        | B | $C_{in}$ | Y             | Y                  | Y              | Y                   |

| 0        | 0        | 0 | 0        | 0             | 0                  |                |                     |

| 1        | 0        | 0 | 1        | 1             | 0                  |                |                     |

| 2        | 0        | 1 | 0        | 1             | 0                  |                |                     |

| 3        | 0        | 1 | 1        | 0             | 1                  |                |                     |

| 4        | 1        | 0 | 0        | 1             | 0                  |                |                     |

| 5        | 1        | 0 | 1        | 0             | 1                  |                |                     |

| 6        | 1        | 1 | 0        | 0             | 1                  |                |                     |

| 7        | 1        | 1 | 1        | 1             | 1                  |                |                     |

**Fonte:** Adaptado de GARCIA e MARTINI, 2018

**c) Represente as saídas (Soma e  $C_{out}$ ) através de trem de pulsos.**

**Resp.:**

**Soma:**

$C_{out}:$

## Circuito Lógico (Subtrator Completo)

Figura 3.4 - Circuito lógico Subtrator completo

Fonte: Autores, 2020

### a) Lógica do Subtrator Completo

De acordo com a Tabela 3.4, verifique que agora temos um carry de entrada ( $C_{in}$ ) e um carry de saída ( $C_{out}$ ). O carry de saída ( $C_{out}$ ) pode ser expresso como uma operação OR de três operações AND entre as variáveis de entrada ( $C_{OUT} = (\bar{A}.B) + (\bar{A}.Cin) + (B.Cin)$ ). Já a saída subtrator apresenta nível lógico “1” apenas quando as variáveis de entrada, A, B e  $Cin$ , não forem iguais e somente em um caso onde as entradas forem todas nível alto “1”, ou seja, pode ser expressa como a operação EX-OR entre as variáveis de entrada (Subtrator =  $A \oplus B \oplus C_{in}$ ) (GARCIA e MARTINI, 2018).

**b)** Após a montagem do circuito lógico subtrator completo, preencha a Tabela 3.4 para efeito comparativo dos valores teóricos com os valores práticos.

Tabela 3.4 - Circuito lógico Subtrator Completo

| Condição | Entradas |   |          | Subtrai(teoria) | $C_{out}$ (teoria) | Subtrai (prática) | $C_{out}$ (prática) |

|----------|----------|---|----------|-----------------|--------------------|-------------------|---------------------|

|          | A        | B | $C_{in}$ | Y               | Y                  | Y                 | Y                   |

| 0        | 0        | 0 | 0        | 0               | 0                  |                   |                     |

| 1        | 0        | 0 | 1        | 1               | 1                  |                   |                     |

| 2        | 0        | 1 | 0        | 1               | 1                  |                   |                     |

| 3        | 0        | 1 | 1        | 0               | 1                  |                   |                     |

| 4        | 1        | 0 | 0        | 1               | 0                  |                   |                     |

| 5        | 1        | 0 | 1        | 0               | 0                  |                   |                     |

| 6        | 1        | 1 | 0        | 0               | 0                  |                   |                     |

| 7        | 1        | 1 | 1        | 1               | 1                  |                   |                     |

Fonte: Adaptado de GARCIA e MARTINI, 2018

**c) Represente as saídas ( $Subtr$  e  $C_{out}$ ) através de trem de pulsos.**

**Resp.:**

**Subtr:**

$C_{out}:$

► **Anexar relatório à experiência, detalhando:**

- Os componentes utilizados e a respectiva pinagem dos CI's;

- Tabelas preenchidas;

- Fotos das etapas durante a montagem do circuito e etapa final;

- Comentários, discussões e dificuldades encontradas.

**Observação:** No final do livro (Anexo) tem um modelo de elaboração de relatório para auxiliar na confecção do mesmo.

## EXPERIMENTO N° 4 DECODIFICADORES

O decodificador é um circuito lógico que recebe um conjunto de entradas, representadas por um número binário, e ativa uma ou mais saídas correspondentes ao número recebido, o qual permite converter o código BCD 8421 (Código decimal codificado em binário) em um código enviado para o display de sete segmentos, onde um número decimal será exibido de acordo com a informação binária nas entradas do decodificador (TOKHEIM, 2013).

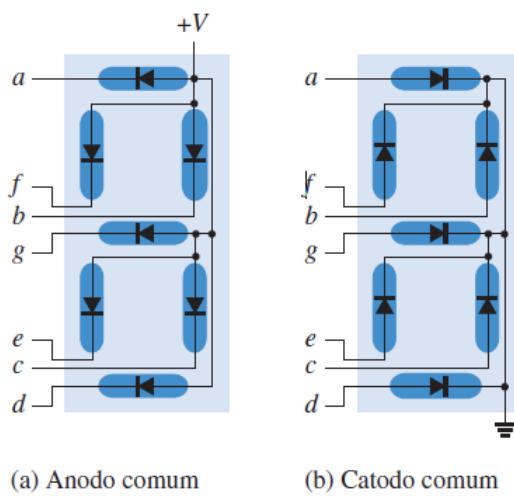

O display de 7 segmentos possui 7 LEDs, num só CI, com uma disposição geométrica padrão, em forma de matriz. Esses segmentos estão arranjados conforme mostra a Figura 4.1, e são identificados por letras que vão de a à g. Sendo cada segmento um LED, pode-se ter dependendo do tipo de montagem interna todos os cátodos conectados juntos (formando um display de configuração tipo cátodo comum) ou todos os ânodos conectados juntos (formando um display de configuração tipo ânodo comum) (TOKHEIM, 2013). A ligação interna de cada um destes displays pode ser representada conforme a Figura 4.2, de forma que cada configuração tem, portanto, sua particularidade e necessita de uma alimentação adequada.

**Figura 4.1-** Configuração interna do display 7 segmentos. (a) Ânodo comum; (b) Cátodo comum

**Fonte:** FLOYD, 2007

Um exemplo típico é o CD4511 um decodificador BCD8421 (*Binary-Coded Decimal*) para 7 segmentos, o qual aceita o código BCD nas suas entradas e os envia para saídas de forma a acionar o display de 7 segmentos para gerar uma leitura decimal de 0 a 9 (FLOYD, 2007).

## OBJETIVOS

- Reconhecer o display de sete segmentos cátodo comum;

- Montar um circuito lógico que converta um sinal binário em decimal (BCD – *Binary Code Decimal*) que será capaz de mostrar os algarismos no display de sete segmentos.

## MATERIAL EXPERIMENTAL

- ProtoBoard;

- Fonte de tensão DC;

- Resistores: 7 x 470Ω;

- Circuito Integrado CMOS: CD4511 – Decodificador;

- Display de 7 segmentos: cátodo comum (C-521G ou equivalente);

- Chaves;

- Alicates;

- Condutores para conexão;

- Multímetro digital.

**Obs.:** A chave simboliza um fio que deve ser ligado a 0 (zero = GND, nível baixo) e 1 (um = Vcc, nível alto).

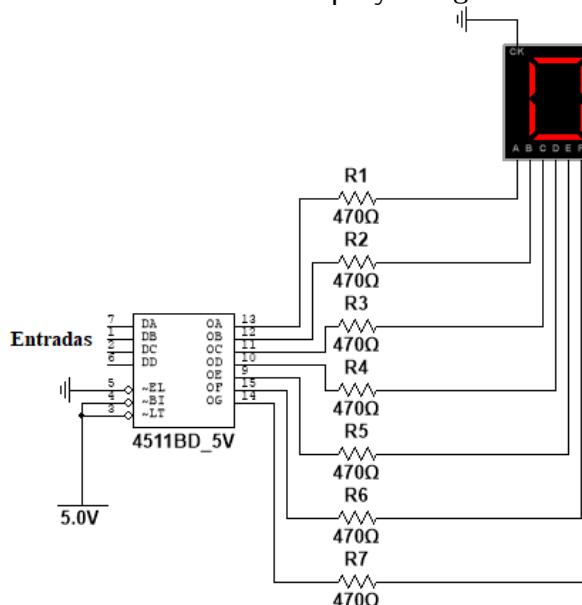

**ATENÇÃO:** A alimentação do circuito integrado é no pino 8 (zero = GND, nível baixo) e no pino 16 (5V) (um = Vcc, nível alto), conforme configuração do CI CD4511 da Figura 4.3.

## PROCEDIMENTO

► Monte o circuito de acordo com a configuração do display na Figura 4.2, não esqueça de alimentar o circuito integrado. Utilize a fonte de alimentação DC da bancada para fornecer a tensão de 5V.

**IMPORTANTE:** Após a montagem chame o(a) professor(a), e peça-o(a) que confira a ligação e, em seguida, energize o circuito.

**Figura 4.2–** Decodificador CD4511 e display 7 segmentos cátodo comum

**Fonte:** Autores, 2020

A Figura 4.3 apresenta o formato dos dígitos no display de 7 segmentos, conforme apresentado no circuito da Figura 4.2 que de acordo com a informação binária nas entradas DA (pino 7), DB (pino 1), DC (pino 2) e DD (pino 6), o display exibirá o algarismo correspondente em decimal.

**Figura 4.3** - Formato dos dígitos no display de 7 segmentos

**Fonte:** Adaptado de TOKHEIM, 2013

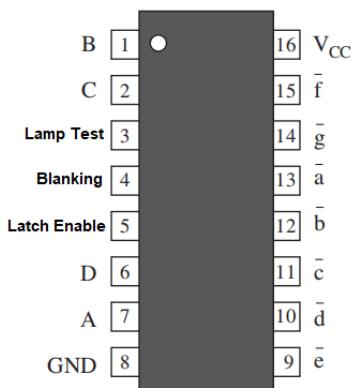

O circuito integrado CD4511 (datasheet) é um decodificador BCD (*Binary-Coded Decimal*) para 7 segmentos, o qual possui 4 pinos de entrada, são eles: pino 1 (B), pino 2 (C), pino 6 (D) e pino 7 (A) e 7 pinos de saída (pino 9 ao pino 15), conforme apresentado na Figura 4.4.

**Figura 4.4** - Pinagem do decodificador CD4511

**Fonte:** Adaptado de FLOYD, 2007

Logo, as entradas de habilitação do decodificador CD4511 são referentes aos pinos 3 (*Lamp Test*), pino 4 (*Blanking*) e pino 5 (*Latch Enable*), segue a função de cada uma dessas em operação normal de acordo com TOKHEIM, (2013):

- **pino 3 (*Lamp Test*):** Representa o teste de lâmpada, serve para testar os segmentos do display. Essa entrada é ligada em nível lógico alto (**1**). Caso a entrada referente ao **pino 3 (*Lamp Test*)** esteja em nível baixo (**0**), todos os segmentos do display irão acender, independente dos níveis lógicos apresentados nas entradas A, B, C e D.

- **pino 4(*Blanking*):** Serve para apagar ou ajustar a intensidade do brilho dos segmentos. Essa entrada é também ligada em nível lógico alto (**1**). Quando a entrada referente ao

**pino 4 (Blanking)** é ativada com um nível baixo (0), todas as saídas tornam-se BAIXAS e todos os segmentos display são apagados.

• **pino 5 (Latch Enable):** Permite armazenar o código de entrada. Essa entrada é ligada em nível lógico baixo (**0**). Caso a entrada referente ao **pino 5 (Latch Enable)** esteja em nível alto (**1**), os níveis lógicos apresentados nas entradas A, B, C e D serão armazenados e o display permanecerá sem alteração, indicando assim o dígito correspondente ao código BCD registrado.

A Tabela 4.1 apresenta o comportamento do decodificador CD4511 juntamente com o display de 7 segmentos, de acordo com os níveis lógicos nas entradas A, B, C e D, o display exibirá o algarismo correspondente em decimal.

► Após a montagem do circuito, realize os testes de acordo com as condições estabelecidas na Tabela 4.1 a seguir preenchendo a tabela com os resultados práticos a fim de comparar com os resultados teóricos.

**Tabela 4.1 - Comportamento do decodificador CD4511**

| Entradas  |          |              |        |        |        |        | Saídas |   |   |   |   |   |   |         |         |

|-----------|----------|--------------|--------|--------|--------|--------|--------|---|---|---|---|---|---|---------|---------|

| Pino 3    | Pino 4   | Pino 5       | Pino 6 | Pino 2 | Pino 1 | Pino 7 | a      | b | c | d | e | f | g | Display | Prática |

| Lamp Test | Blanking | Latch Enable | D      | C      | B      | A      |        |   |   |   |   |   |   |         |         |

| 1         | 1        | 0            | 0      | 0      | 0      | 0      | 1      | 1 | 1 | 1 | 1 | 1 | 0 | 0       |         |

| 1         | 1        | 0            | 0      | 0      | 0      | 1      | 0      | 1 | 1 | 0 | 0 | 0 | 0 | 1       |         |

| 1         | 1        | 0            | 0      | 0      | 1      | 0      | 1      | 1 | 0 | 1 | 1 | 0 | 1 | 2       |         |

| 1         | 1        | 0            | 0      | 0      | 1      | 1      | 1      | 1 | 1 | 1 | 0 | 0 | 1 | 3       |         |

| 1         | 1        | 0            | 0      | 1      | 0      | 0      | 0      | 1 | 1 | 0 | 0 | 1 | 1 | 4       |         |

| 1         | 1        | 0            | 0      | 1      | 0      | 1      | 1      | 0 | 1 | 1 | 0 | 1 | 1 | 5       |         |

| 1         | 1        | 0            | 0      | 1      | 1      | 0      | 0      | 0 | 1 | 1 | 1 | 1 | 1 | 6       |         |

| 1         | 1        | 0            | 0      | 1      | 1      | 1      | 1      | 1 | 1 | 0 | 0 | 0 | 0 | 7       |         |

| 1         | 1        | 0            | 1      | 0      | 0      | 0      | 1      | 1 | 1 | 1 | 1 | 1 | 1 | 8       |         |

| 1         | 1        | 0            | 1      | 0      | 0      | 1      | 1      | 1 | 1 | 0 | 0 | 0 | 1 | 9       |         |

| 1         | 1        | 0            | 1      | 0      | 1      | 0      | 0      | 0 | 0 | 0 | 0 | 0 | 0 | Blank   |         |

| 1         | 1        | 0            | 1      | 0      | 1      | 1      | 0      | 0 | 0 | 0 | 0 | 0 | 0 | Blank   |         |

| 1         | 1        | 0            | 1      | 1      | 0      | 0      | 0      | 0 | 0 | 0 | 0 | 0 | 0 | Blank   |         |

| 1         | 1        | 0            | 1      | 1      | 0      | 1      | 0      | 0 | 0 | 0 | 0 | 0 | 0 | Blank   |         |

| 1         | 1        | 0            | 1      | 1      | 1      | 0      | 0      | 0 | 0 | 0 | 0 | 0 | 0 | Blank   |         |

| 1         | 1        | 0            | 1      | 1      | 1      | 1      | 0      | 0 | 0 | 0 | 0 | 0 | 0 | Blank   |         |

**Fonte:** Adaptado de TOKHEIM, 2013

► **Anexar relatório à experiência, detalhando:**

- Os componentes utilizados e a respectiva pinagem do CI;

- Tabela preenchida;

- Fotos das etapas durante a montagem do circuito e etapa final;

- Comentários, discussões e dificuldades encontradas.

**Observação:** No final do livro (Anexo) tem um modelo de elaboração de relatório para auxiliar na confecção do mesmo.

## EXPERIMENTO N° 5

### CONTADORES

Os contadores variam seus estados de saída segundo o comando do *clock* e de acordo com uma sequência pré-determinada e são projetados com o uso de flip-flops (CARVALHO e SILVA, 2015). As aplicações são designadas para contagens, medição de frequência, divisor de frequência e conversão AD. Os contadores podem ser classificados em assíncronos e síncronos (CAPUANO e IDOETA, 2012).

**Assíncronos** – São estruturas lógicas onde as transições são de forma não sincronizada (GARCIA e MARTINI, 2018). Quando existe o sinal de *clock* aplicado apenas no primeiro estágio, logo os seguintes utilizam como sinal de sincronismo a saída de cada estágio anterior.

**Síncronos** – São estruturas lógicas onde as transições são de forma sincronizada comandadas por um sinal de *clock* externo (GARCIA e MARTINI, 2018). As entradas dos flip-flops são usadas para determinar qual será o novo estágio após cada transição.

O flip-flop JK possui a entrada de *clock*, J e K entrada de dados e as saídas Q (saída de dados armazenada) e (*complemento de Q*), assim como os pinos preferenciais de Set (Preset) e Reset (Clear). A entrada J habilita a transição da saída para nível "um" após o pulso de relógio e a entrada K habilita a transição da saída para nível "zero" após o pulso de relógio. Quando ambas as entradas J e K estão desligadas (zero), o flip-flop não muda de estado e quando ambas entradas J e K estão ligadas (um), as saídas alternam o seu estado a cada pulso de relógio (GARCIA e MARTINI, 2018).

O flip-flop JK é semelhante ao flip-flop Tipo D, esse último será apresentado de forma mais detalhada no Capítulo 6. Diferentemente do flip-flop tipo D, o qual possui uma entrada de dado, o flip-flop JK possui duas entradas J e K para essa finalidade. Ambos flip-flops apresentam uma outra semelhança que são os sinais de Set (Preset) e Reset (Clear) habilitados em nível lógico alto ("1") ou nível lógico baixo ("0"), assim como o pino de *clock*, o qual pode ser ativado com um pulso na borda de subida ou descida. A Figura 5.1 apresenta a simbologia de um flip-flop JK (CARVALHO e SILVA, 2015).

**Figura 5.1** - Simbologia do Flip-flop JK

**Fonte:** CARVALHO e SILVA, 2015

A principal aplicação do flip-flop JK são nos contadores, o qual é ilustrado no diagrama funcional do CI 74LS90, construído esse à partir de quatro flip-flop JK representado na Figura 5.3.

## OBJETIVOS

Montar um circuito lógico que converta um sinal binário em decimal (BCD – *Binary Code Decimal*) que será capaz de mostrar os algarismos no display de sete segmentos e a partir do contador realizar contagem de 0 a 9.

## MATERIAL EXPERIMENTAL

- ProtoBoard;

- Fonte de tensão DC;

- Resistores: 7 x  $470\Omega$ ;

- Circuito Integrado: CD4511 – Decodificador;

- Display de 7 segmentos: catodo comum (C-521G ou equivalente);

- Circuito Integrado: 74LS90 – Contador;

- Chaves;

- Alicates;

- Condutores para conexão;

- Multímetro digital;

- Gerador de *clock*: CI 555; 1 Led;  $R_1: 8,2K\Omega$ ; Potenciômetro:  $100K\Omega$ ;  $C_1: 22\mu F$ ;  $C_2: 0,1\mu F$ .

## PROCEDIMENTO

O 74LS90 é um contador de décadas que pode contar de 0 a  $9_{10}$  (dez algarismos) cicличamente em seu modo natural, ou seja, acompanhar a sequência do código BCD 8421 (CAPUANO e IDOETA, 2012). Consiste de um flip-flop JK e um circuito que divide por 5. Ele conta os pulsos de entrada e sua saída é um número binário de 4 bits através dos pinos  $Q_A$  (pino 12),  $Q_B$  (pino 9),  $Q_C$  (pino 8) e  $Q_D$  (pino 11) conforme configuração da Figura 5.2 do contador 74LS90.

**Figura 5.2** - Configuração do contador 74LS90

**Fonte:** HAUPT e DACHI, 2018

\***Nota:** NC: Nada Conectado

A Figura 5.3 apresenta o Diagrama Funcional em blocos do CI 74LS90 construído a partir de quatro flip-flop JK.

**Figura 5.3 - Diagrama Funcional em blocos do CI 74LS90**

**Fonte:** NETO e OLIVEIRA, 2020

A saída é 0000 em cada décimo pulso e a contagem recomeça do 0 novamente. Um pulso é gerado no pino 9 quando a saída for 0000, seguindo a Tabela 5.1 de contagem do CI 74LS90.

**Tabela 5.1 - Tabela de contagem do CI 74LS90**

| Contagem decimal | Saídas         |                |                |                |

|------------------|----------------|----------------|----------------|----------------|

|                  | Q <sub>D</sub> | Q <sub>C</sub> | Q <sub>B</sub> | Q <sub>A</sub> |

|                  | Pino 11        | Pino 8         | Pino 9         | Pino 12        |

| 0                | 0              | 0              | 0              | 0              |

| 1                | 0              | 0              | 0              | 1              |

| 2                | 0              | 0              | 1              | 0              |

| 3                | 0              | 0              | 1              | 1              |

| 4                | 0              | 1              | 0              | 0              |

| 5                | 0              | 1              | 0              | 1              |

| 6                | 0              | 1              | 1              | 0              |

| 7                | 0              | 1              | 1              | 1              |

| 8                | 1              | 0              | 0              | 0              |

| 9                | 1              | 0              | 0              | 1              |

**Fonte:** Adaptado de GARCIA e MARTINI, 2018

A Tabela 5.2 apresenta o processo de contagem/reset do CI 74LS90. A condição irrelevante (X) representa a situação de entrada em que a saída pode assumir 0 ou 1 indiferentemente, por exemplo, a utilização da condição irrelevante no mapa de Veitch-Karnaugh, onde deve-se adotar o valor (0 ou 1), a escolha do valor terá como finalidade a obtenção de um melhor agrupamento e como consequência uma maior simplificação (CAPUANO e IDOETA, 2012).

**Tabela 5.2 - Tabela de reset/contagem do CI 74LS90**

| Saídas               |                      |                      |                      |                | Entradas Reset          |                         |                         |                         |

|----------------------|----------------------|----------------------|----------------------|----------------|-------------------------|-------------------------|-------------------------|-------------------------|

| <b>Q<sub>D</sub></b> | <b>Q<sub>C</sub></b> | <b>Q<sub>B</sub></b> | <b>Q<sub>A</sub></b> | <b>Decimal</b> | <b>RO<sub>(1)</sub></b> | <b>RO<sub>(2)</sub></b> | <b>Rg<sub>(1)</sub></b> | <b>Rg<sub>(2)</sub></b> |

| <b>Pino 11</b>       | <b>Pino 8</b>        | <b>Pino 9</b>        | <b>Pino 12</b>       | <b>Display</b> | <b>Pino 2</b>           | <b>Pino 3</b>           | <b>Pino 6</b>           | <b>Pino 7</b>           |

| 0                    | 0                    | 0                    | 0                    | 0              | 1                       | 1                       | 0                       | X                       |

| 0                    | 0                    | 0                    | 0                    | 0              | 1                       | 1                       | X                       | 0                       |

| 1                    | 0                    | 0                    | 1                    | 9              | X                       | X                       | 1                       | 1                       |

| Contagem             |                      |                      |                      | 0 a 9          | X                       | 0                       | X                       | 0                       |

| Contagem             |                      |                      |                      | 0 a 9          | 0                       | X                       | 0                       | X                       |

| Contagem             |                      |                      |                      | 0 a 9          | 0                       | X                       | X                       | 0                       |

| Contagem             |                      |                      |                      | 0 a 9          | X                       | 0                       | 0                       | X                       |

**Fonte:** Adaptado de GARCIA e MARTINI, 2018

**\*Nota:** X: condição irrelevante, pode ser 0 ou 1

De acordo com a configuração do contador 74LS90 (Figura 5.2), se o sinal de entrada é conectado à entrada A (pino 14) e a saída Q<sub>A</sub> (pino 12) é conectada a entrada B (pino 1) obtém-se dessa forma um contador de décadas (NETO e OLIVEIRA, 2020).

A Tabela 5.2 apresenta as seguintes condições de operação do contador 74LS90:

- As entradas RO<sub>(1)</sub> e RO<sub>(2)</sub> são entradas *clear*;

- As saídas Q<sub>D</sub>, Q<sub>C</sub>, Q<sub>B</sub> e Q<sub>A</sub> do contador 74LS90 serão todas nível baixo (“0”) sempre que RO<sub>(1)</sub> e RO<sub>(2)</sub> apresentarem nível alto (“1”), desde que uma das entradas Rg apresente nível baixo (“0”), conforme apresentado na Tabela 5.2;

- O contador pode ser pré-setado para uma contagem de 9 (1001) caso Rg<sub>(1)</sub> e Rg<sub>(2)</sub> estejam em nível alto (1);

- Para que contador possa efetuar a contagem normalmente, no mínimo uma das entradas RO e uma das entradas Rg devem apresentar nível baixo (“0”).

## Montagem

- a) As entradas do decodificador CD4511 (A, B, C e D) serão conectadas às saídas do contador 74LS90 (Q<sub>A</sub>, Q<sub>B</sub>, Q<sub>C</sub> e Q<sub>D</sub>) respectivamente, logo a entrada A (pino 14) do contador 74LS90 receberá um pulso do gerador de clock construído através de um Oscilador 555 e em seguida a resposta será direcionada para o display de 7 segmentos, configuração cátodo comum, para que seja realizada a contagem de 0 à 9;

- b) As entradas de habilitação do decodificador CD4511 são representadas pelos pinos 3,4,5 (LT, BI, LE) cuja função já foi descrita na prática do Capítulo 4;

- c) As saídas do decodificador CD4511 permanecem conectadas ao display de 7 segmentos, configuração cátodo comum, conforme já apresentado no Capítulo 4;

- d) A Figura 5.4 apresenta a configuração do contador 74LS90 bem como as ligações que serão conectadas ao decodificador CD4511 cuja configuração deste último encontra-se no Capítulo 4;

- e) A Figura 5.4 mostra a montagem do circuito do gerador de *clock*, o qual será conectado à entrada do pino 14 do contador 74LS90;

- f) Monte o circuito de acordo com a configuração da Figura 5.4, não esqueça de alimentar os circuitos integrados (CD4511 e 74LS90). Utilize a fonte de alimentação DC da bancada para fornecer a tensão de 5V;

- g) Após a montagem chame o(a) professor(a), e peça-o(a) que confira a ligação e, em seguida, energize o circuito;

- h) Para conferência da forma de contagem desse circuito faz-se necessário consultar a Tabela 5.2.

**Figura 5.4** - Configuração da montagem do CI 74LS90 conectado ao CI CD4511

**Fonte:** Autores, 2020

A Figura 5.5 apresenta o diagrama do circuito gerador de *clock*, onde A saída (out) referente ao pino 3 do CI 555 será conectada à entrada do pino 14 do contador 74LS90, a qual fará com que os flip-flops internos trabalhem em cascata para que seja possível efetuar a contagem binária de 0 à 9 nas saídas. Pela contagem quando o contador chegar a 9, automaticamente ocorrerá a parada e o reset do CI, começando um novo ciclo. O sinal positivo é ligado no pino 8 e o sinal negativo no pino 1. O pino 4 permanece ligado no positivo e o pino 5 fica sem conexão (NETO e OLIVEIRA, 2020).

**Figura 5.5 - Gerador de clock com CI 555**

**Fonte:** Autores, 2020

A configuração do CI 555 está representada na Figura 5.6. O circuito gerador de clock (555) deve ser ajustado através do potenciômetro com a velocidade de pulso desejada. O potenciômetro e o capacitor eletrolítico são os responsáveis pela constante de tempo no qual poderá realizar a regulagem do circuito para que ocorra o pulso de clock no intervalo desejado, onde ( $\text{Tempo} = \text{Capacitor} \times \text{resistência do potenciômetro}$ ) (NETO e OLIVEIRA, 2020).

**Figura 5.6 - Configuração do CI 555**

**Fonte:** BRAGA, 2016.

#### ► Anexar relatório à experiência, detalhando:

- Os componentes utilizados e a respectiva pinagem do CI;

- Fotos das etapas durante a montagem do circuito e etapa final;

- Comentários, discussões e dificuldades encontradas.

**Observação:** No final do livro (Anexo) tem um modelo de elaboração de relatório para auxiliar na confecção do mesmo.

## EXPERIMENTO N° 6 FLIP-FLOP TIPO D

São dispositivos de memória que podem armazenar informações binárias em seu circuito interno, os mesmos são derivados dos *latches*, porém ativados pela transição do sinal de controle (borda) (OLANDOSKI, 2016). Isso faz com que um flip-flop permaneça ativado apenas durante um intervalo de tempo pequeno, após a ocorrência de uma transição do sinal de controle.

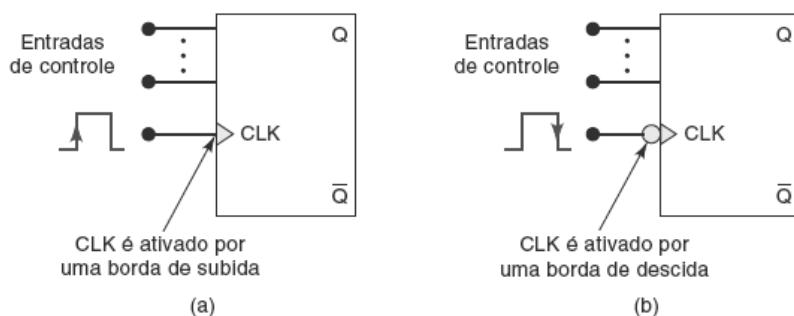

Segundo TOCCI *et. al.* (2011), os sistemas digitais podem operar tanto no modo assíncrono como também no modo síncrono. Nos sistemas assíncronos, as saídas podem alterar de estado a qualquer instante que uma ou mais entradas alterarem. Já nos sistemas síncronos as saídas podem alterar de estado mediante um sinal de *clock*. A depender da construção de um flip-flop, o mesmo pode ser disparado pela transição de subida, onde o *clock* muda de 0 para 1 ou pela transição de descida do sinal de controle quando o *clock* muda de 1 para 0 (Figura 6.1).

**Figura 6.1** - Flip-flops com *clock* têm entrada de *clock* (CLK ) ativada por (a) uma borda de subida ou (b) por uma borda de descida

**Fonte:** TOCCI *et al.*, 2011

De acordo com o funcionamento de suas entradas existem diversos tipos de flip-flops, cujos mais comuns são: SR, T, D e JK.

O Flip-Flop (FF) tipo D (Data or Delay) é o flip-flop mais utilizado, pois o mesmo executa a função de armazenar o valor do bit visualizado na entrada D quando no *clock* é identificada uma transição ascendente (OLANDOSKI, 2016). Pode ser implementado a partir do Flip-Flop JK e um inversor. Para sua aplicação, pode ser usado na transferência de dados.

O FF tipo D armazena o dado de entrada, o mesmo possui um funcionamento semelhante ao FF JK nos pinos Q e CK, porém o armazenamento se comporta de forma diferente, ao invés de termos dois sinais de entrada “J” e “K”, tem-se apenas um sinal “D” e o valor que estiver presente em “D”, seja nível baixo “0” ou nível alto “1”, esse será transferido para a memória interna na mudança de *clock*. A Figura 6.2 apresenta o FF tipo JK e o FF tipo D.

**Figura 6.2 - Flip-Flop (a) JK e (b) D**

**Fonte:** TOCCI *et al.*, 2011

Segundo TOKHEIM (2013) durante a operação síncrona, o Flip-Flop D disparado por borda transfere o bit de dado na entrada D para a saída Q no momento quando há a transição positiva (do nível BAIXO 0 para o nível ALTO 1) do pulso de *clock*. Sendo assim, o flip-flop D 7474 é disparado pela borda positiva.

## OBJETIVO

- Estudar o flip-flop tipo D, analisar e verificar seu funcionamento;

- Entender a atuação das entradas *clock*, *preset* e *clear*.

## MATERIAL EXPERIMENTAL

- ProtoBoard;

- Fonte de tensão DC;

- Resistor:  $470\Omega$ ;

- LEDs: 2;

- Chaves;

- Alicates;

- Condutores para conexão;

- Circuito Integrado: CI 7474 “F-F TIPO D”;

- Multímetro digital.

## PROCEDIMENTO

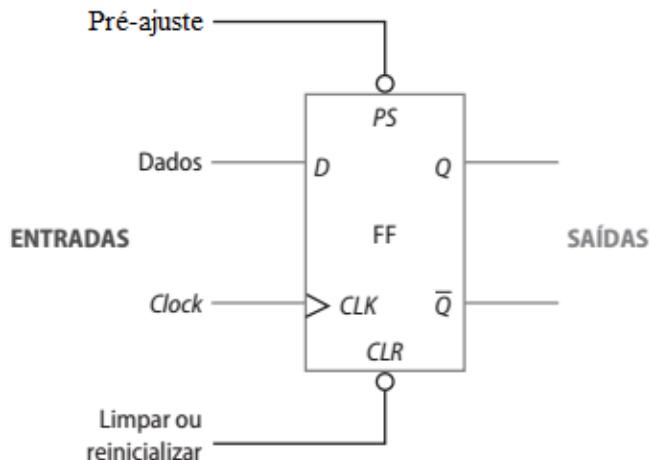

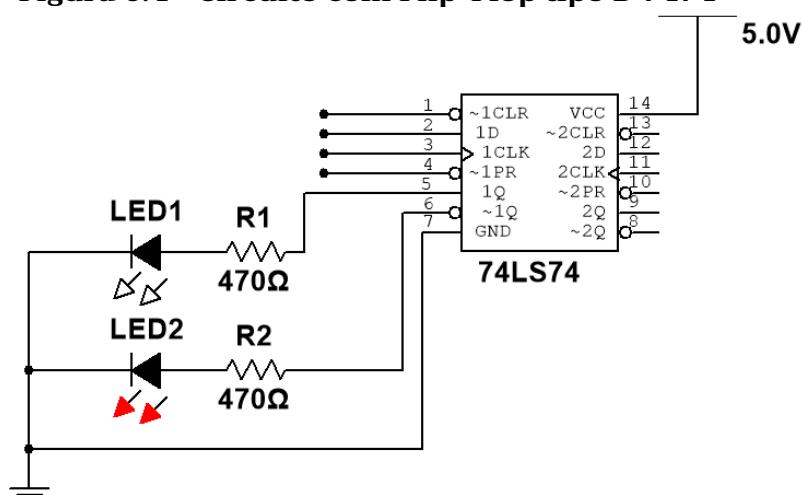

O CI 7474 contém dois flip-flops D idênticos em um DIP de 14 pinos que são independentes um do outro. São disparados por borda positiva e têm entradas assíncronas *preset* e *clear* (FLOYD, 2007). A configuração do CI 7474 está representada na Figura 6.3.

**Obs.:** (A alimentação do CI:  $V_{CC}$  pino 14 e GND pino 7).

**Figura 6.3 - Configuração do Flip-Flop tipo D 7474**

**Fonte:** TOKHEIM, 2013

As entradas de controle do flip-flop tipo D 7474 são denominadas *clock*, *preset* (pré-ajuste), *clear* (limpar ou reiniciar) e dados, as quais permitem um controle sobre as informações de entrada e estabelece sincronismo na operação do circuito. Desse modo, é possível sincronizar o flip-flop (ativar ou desativar) com o intuito de armazenar a informação em qualquer instante e, então, reter a informação armazenada por qualquer período de tempo desejado. As saídas são denominadas Q (1Q) e ( $\sim$ 1Q).

► Monte o circuito da Figura 6.4 e verifique o funcionamento do Flip-Flop tipo “D” com as entradas “*preset*” e “*clear*”.

**IMPORTANTE:** Após a montagem chame o(a) professor(a), e peça-o(a) que confira a ligação e, em seguida, energize o circuito.

**Figura 6.4 - Circuito com Flip-Flop tipo D 7474**

**Fonte:** Autores, 2020

► Preencha a Tabela 6.1 verificando o funcionamento das entradas e saídas do Flip-Flop 7474 de acordo com o comportamento descrito por TOKHEIM (2013).

**Tabela 6.1 - Funcionamento das entradas e saídas do CI 7474**

| Modo de operação           | Entradas |        |        |        | Saídas<br>(Teoria) |           | Saídas<br>(Prática) |           |

|----------------------------|----------|--------|--------|--------|--------------------|-----------|---------------------|-----------|

|                            | Preset   | Clear  | Clock  | D      | Pino 5             | Pino 6    | Pino 5              | Pino 6    |

|                            | Pino 4   | Pino 1 | Pino 3 | Pino 2 | <i>Q</i>           | $\bar{Q}$ | <i>Q</i>            | $\bar{Q}$ |

| Inicialização assíncrona   | 0        | 1      | X      | X      | 1                  | 0         |                     |           |

| Reinicialização assíncrona | 1        | 0      | X      | X      | 0                  | 1         |                     |           |

| Proibido                   | 0        | 0      | X      | X      | 1                  | 1         |                     |           |

| Inicialização              | 1        | 1      | ↑      | 1      | 1                  | 0         |                     |           |

| Reinicialização            | 1        | 1      | ↑      | 0      | 0                  | 1         |                     |           |

**Fonte:** Adaptado de TOKHEIM, 2013